# **Master of Computer Application**

(Open and Distance Learning Mode)

Semester – I

# **Computer Organization and Architecture**

# **Centre for Distance and Online Education (CDOE)**

DEVI AHILYA VISHWAVIDYALAYA, INDORE

"A+" Grade Accredited by NAAC

IET Campus, Khandwa Road, Indore - 452001 www.cdoedavv.ac.in www.dde.dauniv.ac.in

### **Program Coordinator**

#### **Dr. Anand More**

School of Computer Science and IT Devi Ahilya Vishwavidyalaya, Indore – 452001

### **Content Design Committee**

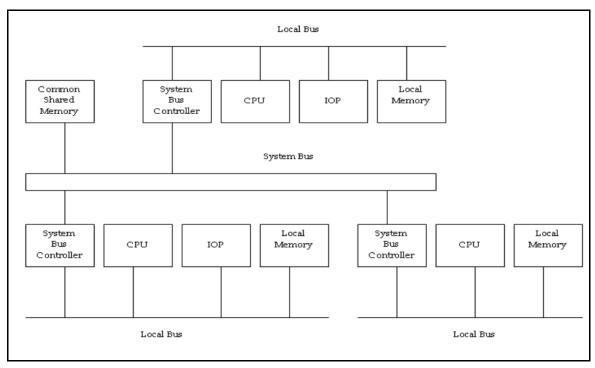

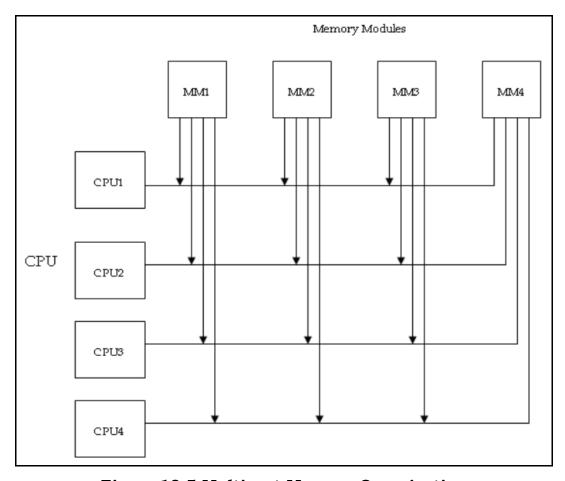

### **Dr. Pratosh Bansal**

Centre for Distance and Online Education Devi Ahilya Vishwavidyalaya, Indore – 452001

### Dr. C.P. Patidar

Institute of Engineering & Technology

Devi Ahilya Vishwavidyalaya, Indore – 452001

### Dr. Shaligram Prajapat

International Institute of Professional Studies Devi Ahilya Vishwavidyalaya, Indore – 452001

### **Language Editors**

### Dr. Arti Sharan

Institute of Engineering & Technology

Devi Ahilya Vishwavidyalaya, Indore – 452001

### Dr. Ruchi Singh

Institute of Engineering & Technology

Devi Ahilya Vishwavidyalaya, Indore – 452001

### SLM Author(s)

### Mr. Mohit Verma

M.C.A.

SCS, Devi Ahilya Vishwavidyalaya, Indore – 452001

### Mr. Ashish Panchal

B.E., M.E.

IET, Devi Ahilya Vishwavidyalaya, Indore – 452001

**Copyright**: Centre for Distance and Online Education (CDOE), Devi Ahilya Vishwavidyalaya

**Edition**: 2022 (Restricted Circulation)

Published by : Centre for Distance and Online Education (CDOE), Devi Ahilya Vishwavidyalaya

Printed at : University Press, Devi Ahilya Vishwavidyalaya, Indore – 452001

| Compute | Organization & Architectu | ıre |

|---------|---------------------------|-----|

|         |                           |     |

|         |                           |     |

# **Table of Contents**

### Introduction

| <b>MODUI</b> | .E. I          | INTRO     | DITC  | MOI |

|--------------|----------------|-----------|-------|-----|

| MODUL        | <i>1</i> 12. I | 111 1 1// | JDUUJ |     |

| Unit 1 | 1 _ 1 | Intro | duc | tion |

|--------|-------|-------|-----|------|

| .,     | _     |       |     |      |

- 1.0 Introduction

- 1.1 Unit Objectives

- 1.2 Digital Computers

- 1.3 Von Neumann Computers

- 1.4 Basics of Computer Architecture and Organization

- 1.5 History of Computers

- 1.6 Operational Concept

- 1.7 Summary

- 1.8 Key Terms

- 1.9 Check Your Progress

### Unit 2 - Digital Logic Circuits

- 2.0 Introduction

- 2.1 Unit Objectives

- 2.2 Boolean Algebra

- 2.2.1 Boolean Operators

- 2.2.2 Truth Table

- 2.2.3 Boolean Identities

- 2.3 Logic Gates

- 2.3.1 Common Logic Gates

- 2.3.2 Universal Gates

- 2.3.3 Combinational Gates

- 2.4 K- Map Simplification

- 2.5 Combinational Circuits

- 2.5.1 Decoder

- 2.5.2 Multiplexer

- 2.6 Arithmetic Circuits

- 2.7 Sequential Circuits

- 2.7.1 Basic Latch

- 2.7.2 Flip- Flop

- 2.8 Registers and Counters

- 2.9 Summary

- 2.10 Key Terms

- 2.11 Check Your Progress

### **MODULE: II - COMPUTER ARITHMETIC AND MICROOPERATIONS**

# Unit 3 - Computer Arithmetic

- 3.0 Introduction

- 3.1 Unit Objectives

- 3.2 Data Representation

- 3.2.1 Conversion Techniques

- 3.3 Addition and Subtraction of Binary Numbers

- 3.3.1 Two's Complement Method

- 3.4 Multiplication of Binary Numbers

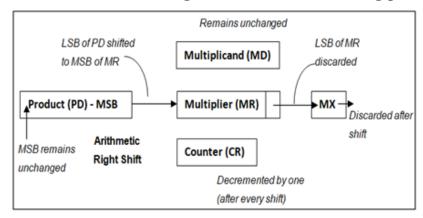

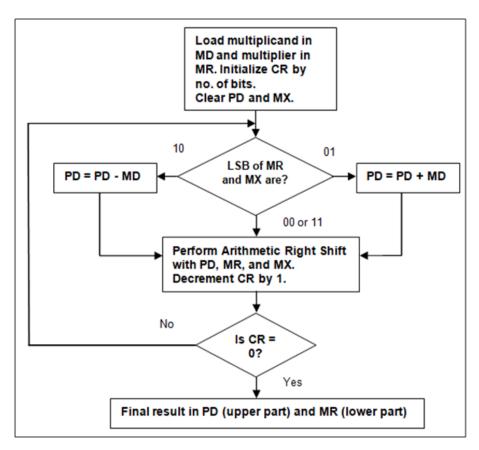

- 3.4.1 Booth's Algorithm

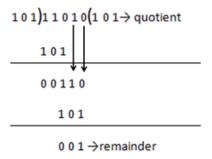

- 3.5 Division of Binary Numbers

- 3.6 Floating-Point Number Representation

- 3.7 Floating-Point Arithmetic and Unit Operations

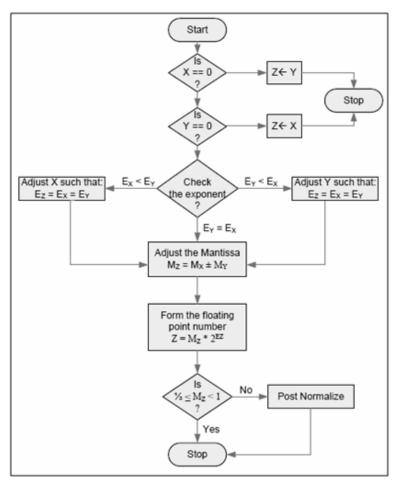

- 3.7.1 Floating-point Addition and Subtraction

- 3.7.2 Floating-point Multiplication

- 3.7.3 Floating-point Division

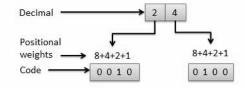

- 3.8 Binary Codes and Error Detection Codes

- 3.9 Summary

- 3.10 Key Terms

- 3.11 Check Your Progress

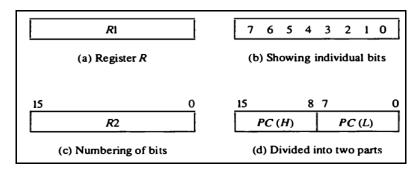

### Unit 4 - Register Transfer and Microoperations

- 4.0 Introduction

- 4.1 Unit Objectives

- 4.2 Register Transfer Language

- 4.3 Register Transfer

- 4.4 Bus and Memory Transfers

- 4.5 Bus and Memory Transfers

- 4.6 Logic microoperations

- 4.7 Shift microoperations

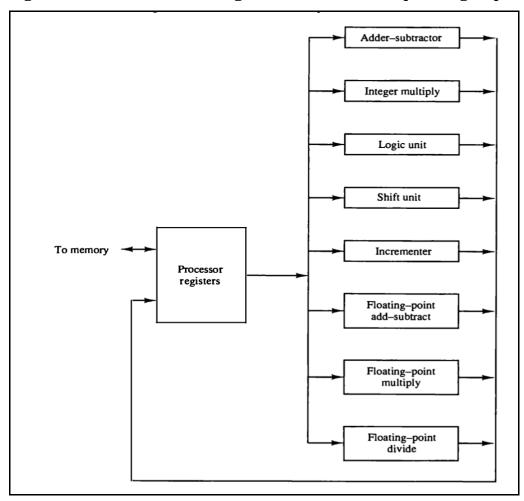

- 4.8 Arithmetic Logic Shift Unit

- 4.9 Summary

- 4.10 Key Terms

- 4.11 Check Your Progress

# Module: III – BASIC COMPUTER ORGANIZATION, DESIGN AND PROGRAMMING

# Unit 5 – Basic Computer Organization and Design

- 5.0 Introduction

- 5.1 Unit Objectives

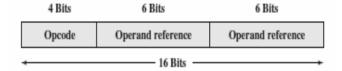

- 5.2 Instruction Codes

- 5.3 Register Sets

- 5.4 Instruction Sets

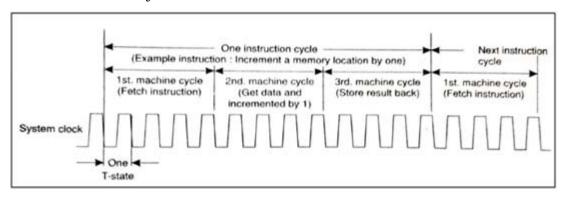

- 5.5 Machine Cycle, Timings and Control

- 5.6 Input- Output and Interrupts

- 5.7 Basic Computer Design

- 5.8 Design of Accumulator Logic

- 5.9 Summary

- 5.10 Key Terms

- 5.11 Check Your Progress

### Unit 6 - Programming the Basic Computer

- 6.0 Introduction

- 6.1 Unit Objectives

- 6.2 High Level, Assembly, and Machine Language

- 6.2.1 High Level Language

- 6.2.2 Assembly Language

- 6.2.3 Machine Language

- 6.3 Assembler

- 6.4 Programming Arithmetic & Logic Operations

- 6.5 Subroutines

- 6.6 Input- Output Programming

- 6.7 Summary

- 6.8 Key Terms

- 6.9 Check Your Progress

### Module: IV - CENTRAL PROCESSING UNIT AND MEMORY ORGANIZATION

# **Unit 7 - Central Processing Unit**

- 7.0 Introduction

- 7.1 Unit Objectives

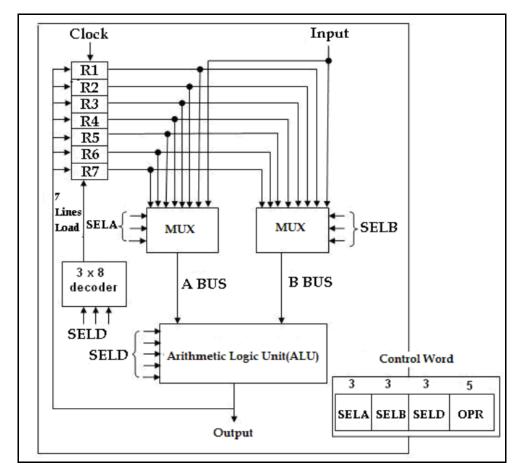

- 7.2 General Register Organization

- 7.3 Stack Organization

- 7.4 Instruction Formats

- 7.5 Addressing Modes

- 7.6 Types of Instructions

- 7.7 Reduced Instruction Set Computer (RISC)

- 7.8 Summary

- 7.9 Key Terms

- 7.10 Check Your Progress

# Unit 8 - Memory Organization

- 8.0 Introduction

- 8.1 Unit Objectives

- 8.2 Memory Classification

- 8.2.1 Read Only Memory (ROM)

- 8.2.2 Read/ Write Memory (RAM)

- 8.3 Memory Characteristics and Hierarchy

- 8.3.1 Cache Memory

8.3.2 Main Memory

8.3.3 Secondary Memory

8.3.4 Virtual Memory

- 8.4 Memory Management Hardware

- 8.5 Memory Decoding

- 8.6 Summary

- 8.7 Key Terms

- 8.8 Check Your Progress

### Unit 9 - Control Unit

- 9.0 Introduction

- 9.1 Unit Objectives

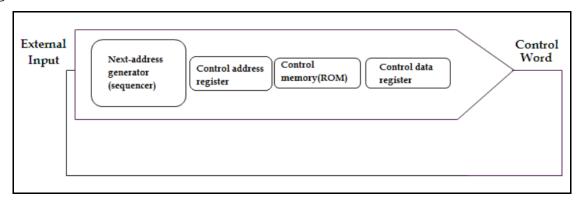

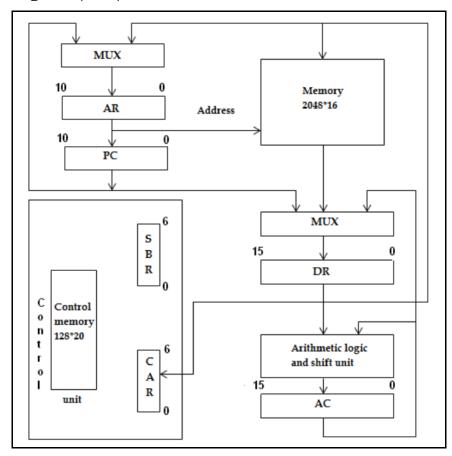

- 9.2 Control Memory

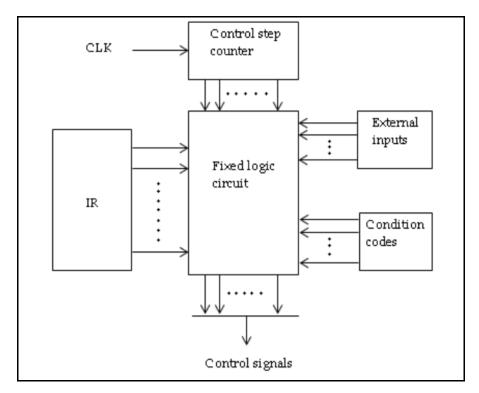

- 9.3 Hardwired Control and Micro Programmed Control Unit

- 9.3.1 Micro Programmed Control

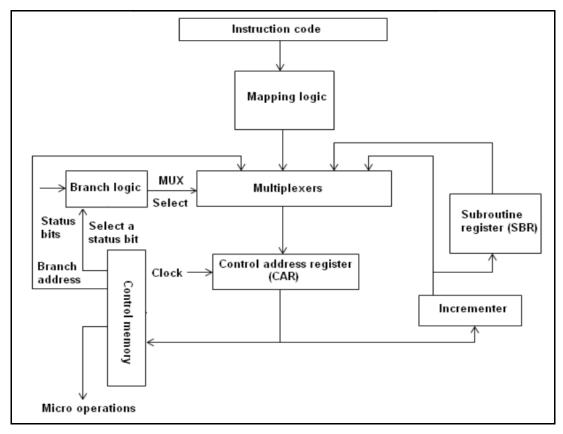

- 9.4 Address Sequencing

- 9.4.1 Conditional Branching

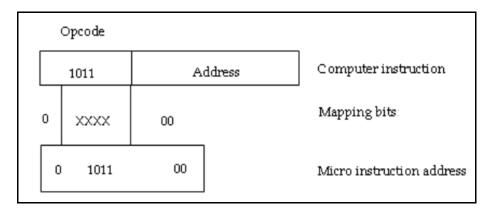

- 9.4.2 Instruction Mapping

- 9.4.3 Subroutines

- 9.5 Microprogram Sequencing

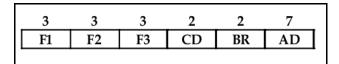

- 9.5.1 Micro Instruction Format

- 9.5.2 Symbolic Micro Instructions

- 9.6 Summary

- 9.7 Key Terms

- 9.8 Check Your Progress

# Module: V- INPUT/ OUTPUT ORGANIZATION, PARALLEL PROCESSING AND MULTIPROCESSORS

# Unit 10 - Input/ Output Organization

- 10.0 Introduction

- 10.1 Unit Objectives

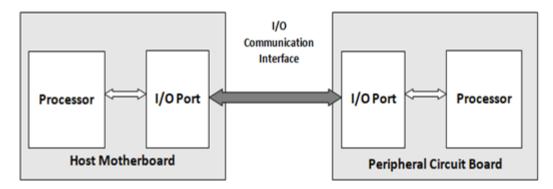

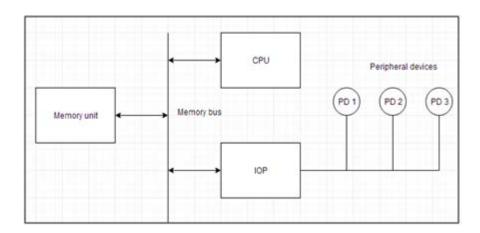

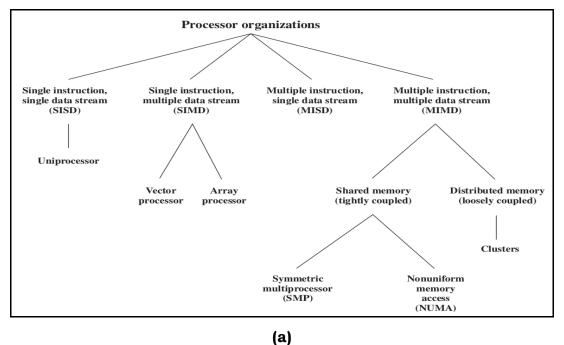

- 10.2 Basic Input/ Output Structure of Computers

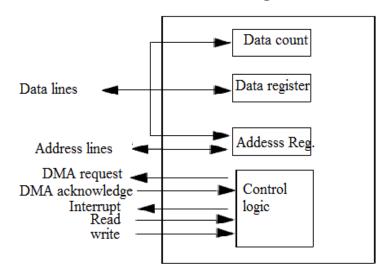

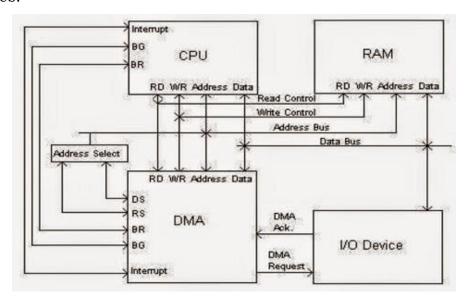

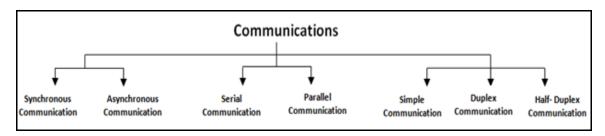

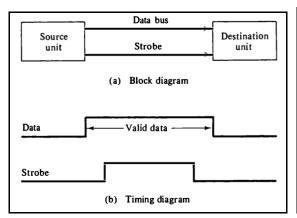

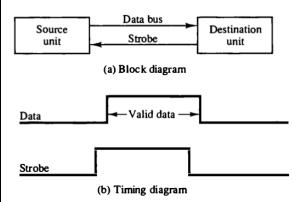

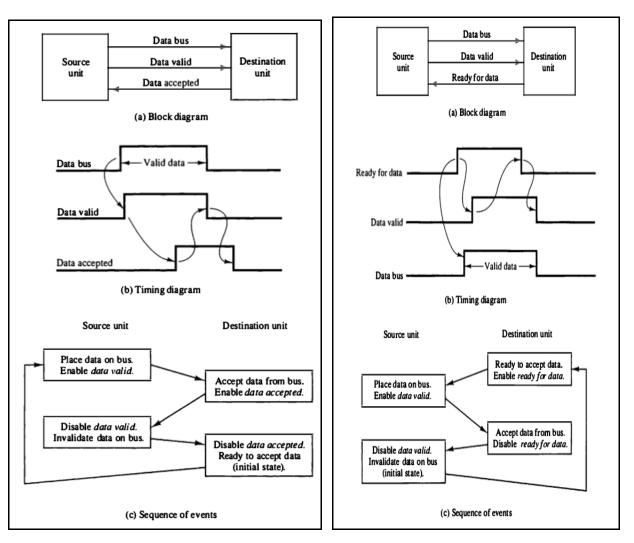

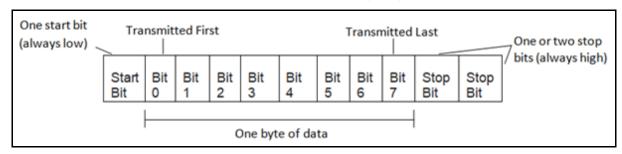

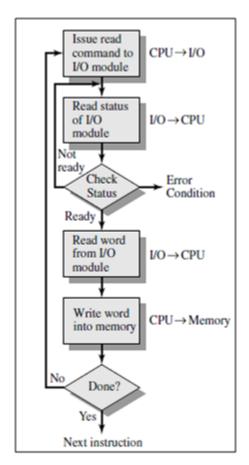

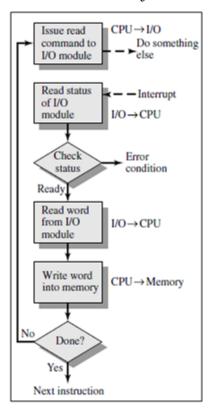

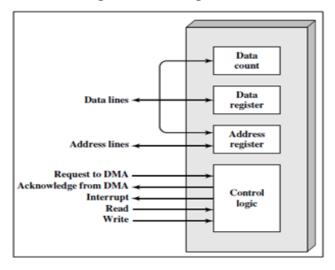

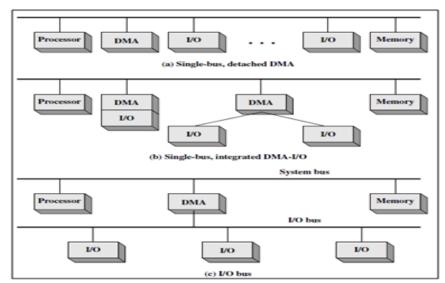

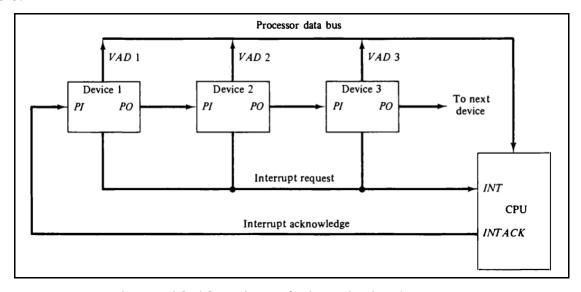

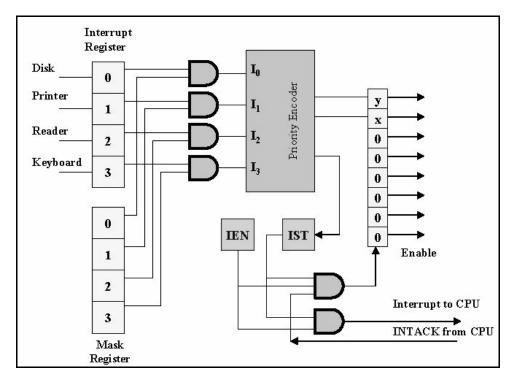

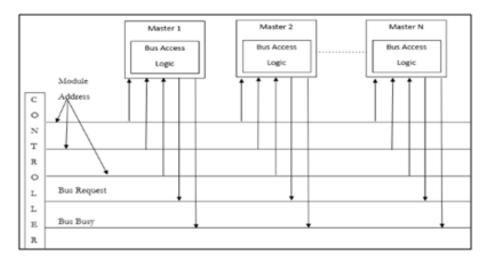

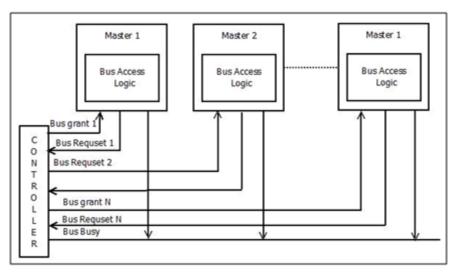

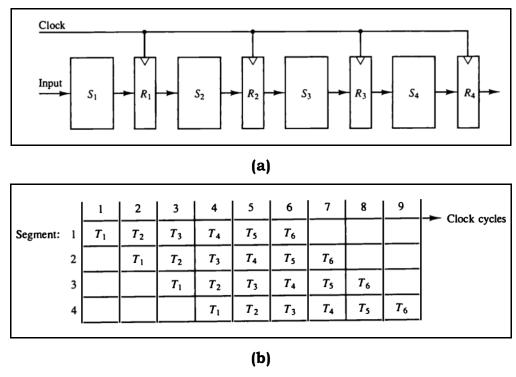

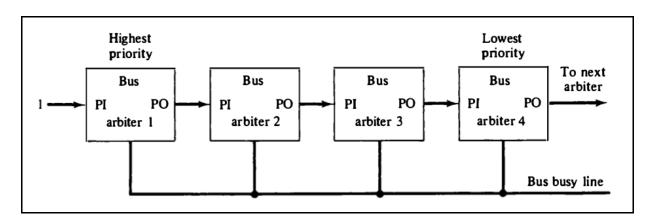

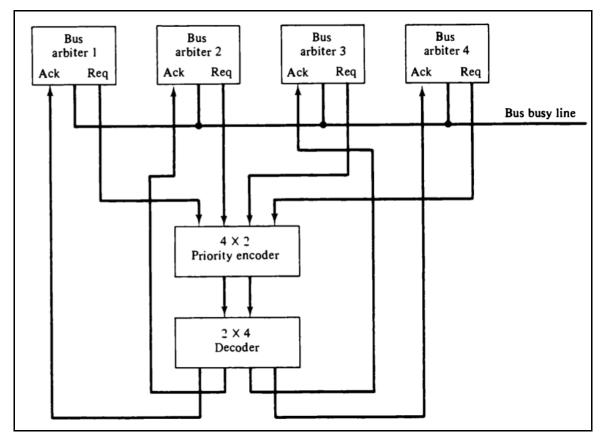

- 10.3 Synchronous and Asynchronous Data Transfer 10.3.1 Strobe Control 10.3.2 Handshaking 10.4 Serial and Parallel Communication 10.5 Modes of Transfer 10.5.2 Interrupt Driven I/O 10.5.1 Programmed I/O (Polling) 10.5.3 Direct Memory Access (DMA) 10.6 Priority Interrupt 10.6.1 Daisy- Chain Priority 10.6.2 Parallel Priority Interrupt 10.6.3 Priority Encoder 10.7 Device Drivers 10.8 Standard I/O Interfaces (Buses) 10.9 Bus Arbitration 10.10 I/O Processor 10.11 Summary 10.12 Key Terms 10.13 Check Your Progress **Unit 11 – Parallel Processing** 11.0 Introduction 11.1 Unit Objectives 11.2 Parallel Processing 11.3 Pipelining 11.4 Data Dependency 11.5 Handling of Branch Instructions

- 11.8 Summary

11.6 Vector Processing

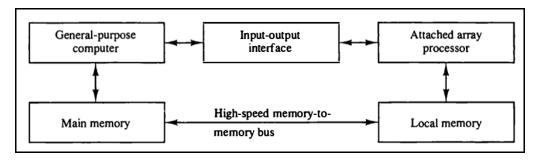

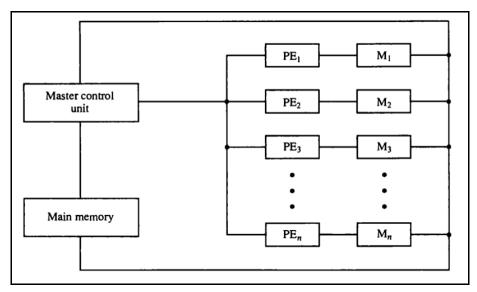

11.7 Array Processors

- 11.9 Key Terms

- 11.10 Check Your Progress

# **Unit 12 - Multiprocessors**

- 12.0 Introduction

- 12.1 Unit Objectives

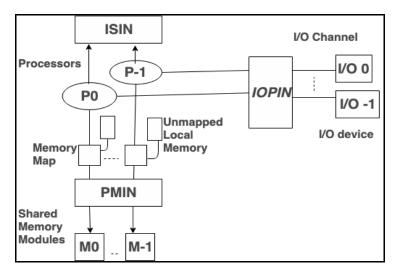

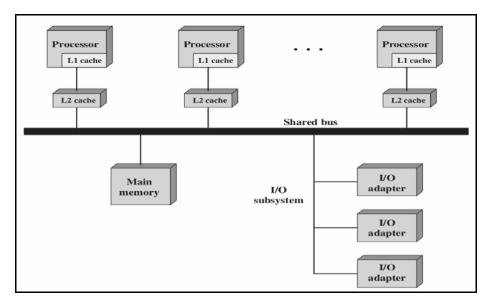

- 12.2 Characteristics of Multiprocessors

- 12.3 Types of Multiprocessors

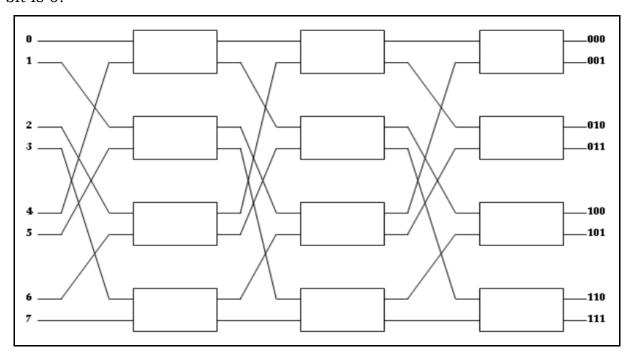

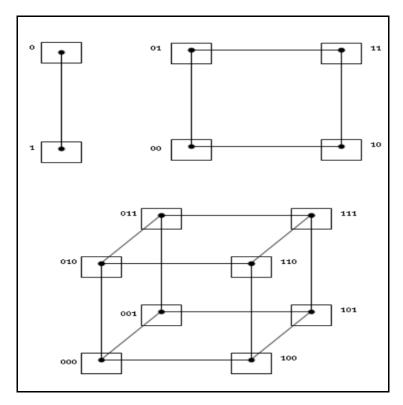

- 12.4 Interconnection Structures

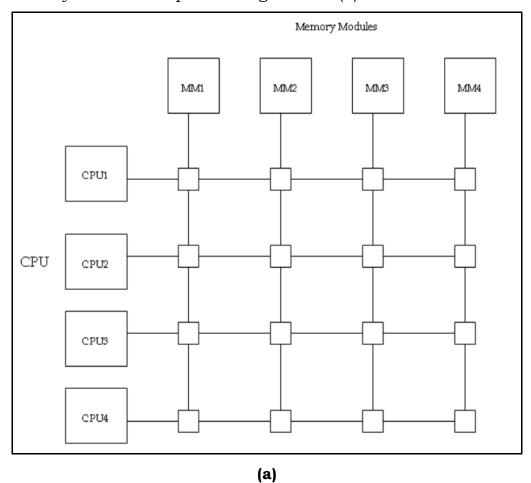

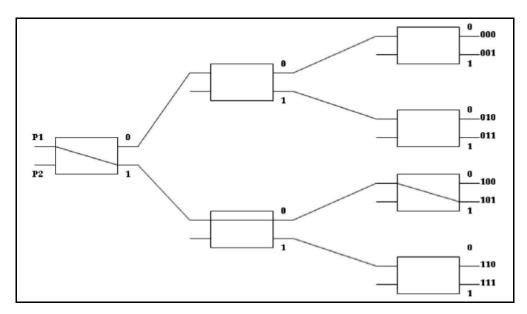

- 12.4.1 Time-Shared Common Bus 12.4.2 Multiport Memory

- 12.4.3 Crossbar switch

- 12.4.4 Multistage switching network

- 12.4.5 Hypercube system

- 12.5 Interprocessor Arbitration

- 12.5.1 Serial Arbitration Procedure 12.5.2 Parallel Arbitration Logic

- 12.5.3 Dynamic Arbitration Algorithms

- 12.6 Inter-Processor Communication And Synchronization

- 12.7 Symmetric Multiprocessors

- 12.8 Summary

- 12.9 Key Terms

- 12.10 Check Your Progress

#### INTRODUCTION

Today technology has made its roots in the day to day life of humans. We use computers in every way possible or rather we have become completely dependent on computers by now. A normal being is just concerned about the work the computer does for him but unaware of the internal operations, functions, and programs of the computer system. It is essential to have an insight into how the computer system works. Computer Organization and Architecture deal with the study of internal working, structuring distinct functional modules, and implementation of a computer system. Computer Architecture means to design the basic structure of a computer system while computer organization is concerned with the practical implementation of this carefully designed computer architecture in terms of hardware attributes.

This study material reveals the basic internal structure and functioning of a modern-day computer system. The evolution of technology from vacuum tubes based computers to supercomputers, historical background, and operational concept of computers, Von Neumann's structure of computers are discussed in Module-1 of this course. It also explains the fundamentals of the digital logic circuits, Boolean algebra, map simplification, different logic gates, and different logical circuits. This helps in gaining knowledge about the basic circuits like combinational and sequential circuits and logics involved in designing a computer system.

Unit- 3 and 4 of Module: II gives an extended outlook on the basic computer arithmetic operations including different techniques to perform addition, subtraction, multiplication, and division of binary numbers (signed and unsigned). The module also depicts the basic features of a Register transfer language and different microoperations.

The next module, i.e. Module: III illustrates the basics of the computer processor, its architecture, and organization. It explains the concept of instructions, interrupts, register sets, stack organization, and machine cycles to make the readers understand how the internal circuitry of a computer

works. Unit-6 of this module follows the concept of programming in the computer system. It focuses on the concept of High- level, machine, and assembly language programming, subroutines, Input-output programming of the processor.

In Unit- 7 and 8 of Module: IV, the different Addressing modes and discussion about reduced instruction set computing (RISC) and complex instruction set computing (CISC) types of processors are elucidated. The discussion follows the memory system of a computer in detail. The memory classification including ROM, RAM, cache memory, and virtual memory are featured in the module.

Module: V illustrates the detailed discussion about the Input-Output Unit and the internal structure of the control unit of the computer. The fundamental characteristics of data transfer through Programmed I/O, Interrupt driven I/O, and Direct Memory Access (DMA) are explained in the module. It also elaborates on the basic characteristics of multiprocessors. Parallel Processing and Multiprocessors are also discussed in Unit-10 and 11 respectively.

This content is designed comprehensively and follows a simple approach, keeping in mind the syllabus of the program. It exhilarates interest and is sure to stimulate knowledge among the readers. The purpose is to acquaint the readers with the principle and design of computer organization and architecture. Numerous figures and tables, key terms help in simplifying learning about the subject. The 'Check Your Progress' section intends the readers to test their knowledge. It is hoped that the language and the content demonstration is coherent to the readers and will enhance their learning in the best way possible.

MODULE: I INTRODUCTION

### Structure

- 1.0 Introduction

- 1.1 Unit Objectives

- 1.2 Digital Computers

- 1.3 Von Neumann Computers

- 1.4 Basics of Computer Architecture and Organization

- 1.5 History of Computers

- 1.6 Operational Concept

- 1.7 Summary

- 1.8 Key Terms

- 1.9 Check Your Progress

### 1.0 Introduction

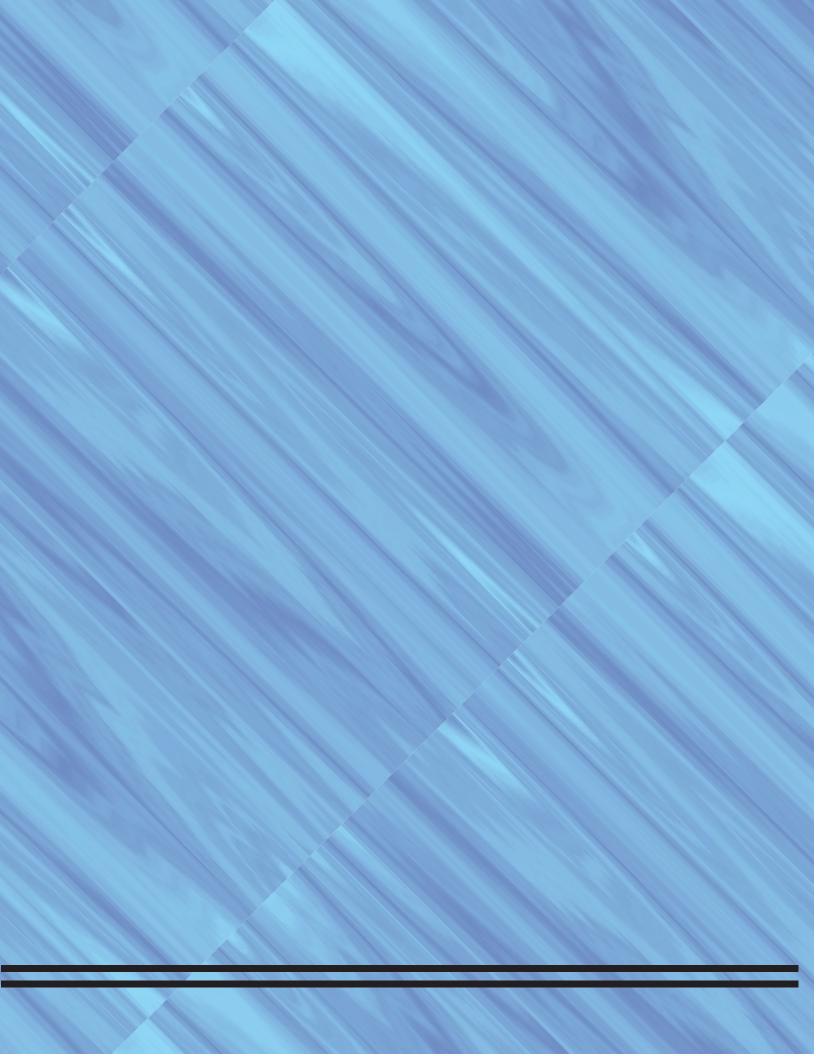

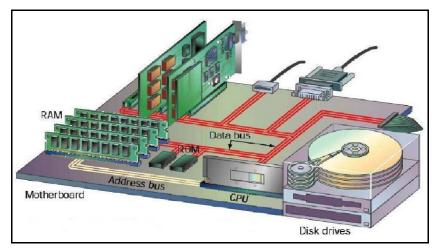

With the advancement in science and technology, the computer has become an essential need for humans. We are totally dependent on computers for the day to day work in different ways. There is hardly any field which is not affected by computers. The basic and theoretical definition of a computer is not unfamiliar with this world. It is stated that a computer is an electronic machine that performs different operations as per the need of the user. The raw data as an input is provided to the computer through input devices, then the processor processes this data by performing various operations, and finally, the output is obtained from the output devices by the user. However, it is strange that even among some present-day people; there is minimum awareness about the overall working mechanism of a computer, although these people may be daily using a computer in any manner like laptops, mobiles, notepads, etc. They continue with a mindset that the detailed knowledge of computer architecture and structure is confined to computer engineers and others related to the information technology stream, but it is not so. The basic working mechanism is studied under Computer Organization and Architecture. Figure 1.1 shows

the basic computer architecture that comprises Input and Output devices; Central Processing Unit (CPU) that is subdivided into Control Unit (CU) and Arithmetic Logic Unit (ALU); Main memory and external storage. Each block contributes to different functions of the system, which we will discuss in the following units.

Figure 1.1 Basic Computer Architecture

### 1.1 Unit Objectives

On completion of this unit, one will be able to:

- Gain knowledge about the basics of computers and its fundamentals.

- Discuss the brief history of the evolution of computers.

- Learn the general operational concepts of a computer.

### 1.2 Digital Computers

Digital computers refer to the computer system that operates on the concept of discrete numbers. They are generally used for numerical applications of the computer system. Digital computers work on the binary number system, having two states 0 and 1. The smallest unit of the binary number system is a bit. Group of bits represents any form of information in the system. Different coding techniques are used to perform various operations in digital computers. A complete set of instructions can be represented using a group of bits to perform any type of operation.

A basic computer functions using two entities: software and hardware. The

hardware part includes all the peripheral devices (input and output) connected to the computer and have physical appearance for the users. On the other hand, the software refers to the internal programs and instructions that are processed by the computer. A computer program is a combination of a set of instructions to be processed by the computer. All the computer programs require a basic platform for proper functioning and this interface between the computer and the user is known as the operating system.

Computer architecture and organization are two slightly different aspects in terms of definitions. Computer architecture generally includes design-related issues while computer organization deals with the implementation of the architectural modules. Computer designing and implementation is generally related to the hardware designing of the system. It takes an account of what and how hardware should be connected in a system. Computer architecture is basically concerned with the internal structure of the computer including the format of information, instruction sets, memory management, etc. It can be observed that during the passing years, there was not much change in the architecture of a computer but its organization has sustained various changes and is still continuing. We will discuss the history or evolution of computers, for a better understanding of these changes in the organization.

### 1.3 Von Neumann Computers

The early day's computers were bound to process one instruction at a time and most of the time the instructions were loaded in the system manually by the operators. It was time taking and less effective. Due to the absence of any provision to store the instructions to be executed later, it was more difficult. The function of such computers was very specific and fixed. It was not possible to program them regularly, for example, calculators.

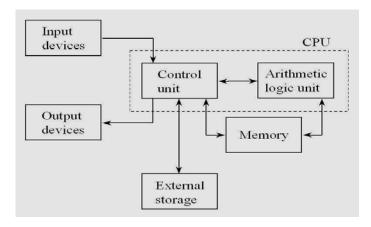

To overcome this issue, in 1945, John Von Neumann Architecture came to the rescue. According to the Von Neumann architecture, one can encode and even store the instructions in the memory of the computer so that they can be executed whenever required. While executing any program, the desired

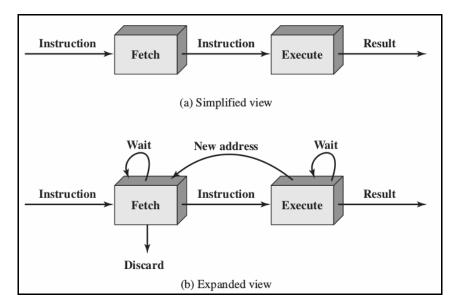

instruction is fetched from the memory and then decoded to generate the required output. Figure 1.2 shows the basic structure of Von Neumann architecture. As depicted from the figure, it can be observed that the control unit is being considered as a part of the processor only. The control unit generates control signals that are responsible for the proper functioning of the instructions of the computer system. The fetching, decoding, and execution of instructions from the memory reduce the execution time and impart faster speed to the computer system. This cycle of instructions in the Neumann architecture is termed as *instruction cycle*.

Figure 1.2 Basic structure of Von Neumann Architecture of Computer

Von Neumann architecture proved to be a revolution since its introduction. It formed the basis for computer designing for several decades. The only issue with this architecture was that only one instruction was being fetched at a time, or the memory could be accessed only once a while. As this architecture was deprived of sequential instruction execution, this state was referred to as 'Von Neumann Bottleneck'. The data and instructions both are stored in the same memory and use the same bus for data transfer. This can result in low-performance computations.

To overcome the above mentioned drawback of Von Neumann architecture, *Harvard Architecture* was considered. Harvard architecture comprises separate storage and signal path for data and instruction. This results in simultaneous instruction execution and data processing.

### 1.4 Basics of Computer Architecture and Organization

We all are aware of the external structure of a personal computer or desktop that contains input devices such as a keyboard or a mouse; output devices like monitor display screen or a printer; and a CPU. Different types of computers can be seen at different places depending upon their need, for example, a workstation can be seen at some designer's office where the basic computer is attached to other peripherals like scanner and digitizer. Here, we will discuss an overview of the computer hardware briefly, used in the basic computer architecture shown in Figure 1.1. Let us first discuss the basic working of a computer.

- **Input Devices:** Like any other machine, it is required by the computer to get the prior instructions and data from the user to process the information. The input devices are used to feed instructions, data, and programming to instruct the computer to perform the required function on the input data. The commonly used input devices are keyboard, mouse, touchpad, scanner, microphone, disks, etc.

- **Processing:** The process of performing operations and functions on the raw data provided by the user is known as the processing of data. The CPU performs all the required operations and calculations with the help of ALU. The control unit (CU) controls all these operations. The result of the processed data is then provided to the user via output devices and also stored in the primary storage of the computer.

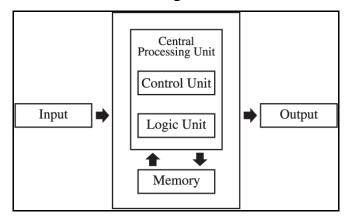

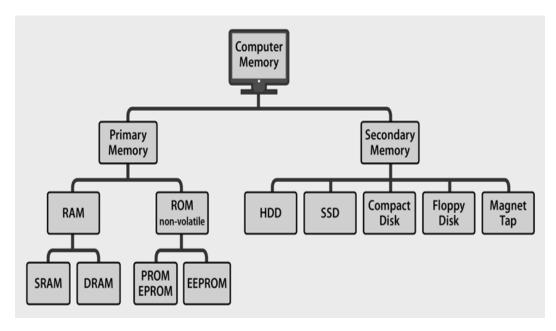

- Storage: It is essential for the computer to store the data which it has to process and which it has already processed. Some data is to be stored permanently while some are meant to be stored temporarily. On this basis, the storage unit is subdivided into two types: Primary Storage and Secondary Storage. Primary storage is the internal memory of the computer that is temporary and small in size while secondary storage has large storage capacity and they store the data permanently. Figure 1.3 shows the basic classification of the memory of the computer. Primary storage includes RAM (Random Access Memory) and ROM (Read

Only Memory). RAM is volatile memory i.e. it gets erased when the power is switched off while ROM is a non-volatile memory i.e. it stores the data permanently and retains the data even if the power gets off. The CPU can only read the contents of ROM and cannot edit it while the content of RAM can be read and written both by the CPU whenever required. The primary memory also includes the Cache memory and Registers which are used to store the data internally and are temporary in nature.

Figure 1.3 Classification of Computer Memory

The secondary storage devices include Hard disk drives (HDD), memory cards, compact disks (CD), floppy disks, and magnetic tapes.

- **Output Devices:** The output devices are used to display the result of the processed data to the user. The result can be in an audio, visual, or printed form. The most common output devices are monitor display and printer. Other output devices are a projector, speakers, headphones, etc.

- **Power Supply:** The power supplied to the computer depends upon its type and size. Earlier computers used more power and slowly with the decrease in size, the power consumption of the computer also decreased. The Power Supply Unit (PSU) is the internal power unit of the computer that modulates the main AC supply to a low-voltage DC power supply. Switched Mode Power Supply (SMPS) is the popular power supply used by modern computers.

Motherboard: It is the main circuit board of the computer in the form of

a printed circuit board. It comprises a microprocessor and other

necessary components that are interconnected with the help of cables.

The motherboard provides an interface between the input/ output

devices and the storage of the computer.

Figure 1.4 Motherboard and other functional units of a computer

(**Source-** https://www.slideshare.net/mobile/AmosNdubi/how-computers-transform-data-to-information-lesson-3-bso)

# 1.5 History of Computers

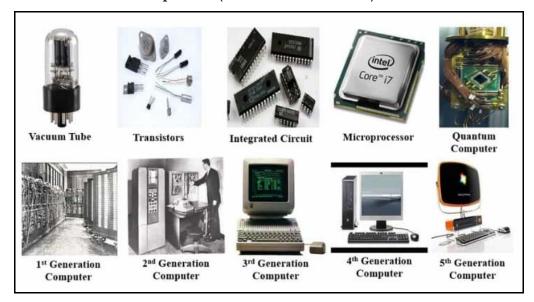

The present scenario of computers is more accessible, accurate, user-friendly, speedy, simple, compact, and easy to use. However, the earlier picture was much different. The earlier generations of computers were complex and time taking. The foremost step towards automatic computing was taken by the well-known European scientist, **Pascal**, long back in 1642 when he fabricated a mechanical calculating machine, which was capable of only addition and subtraction. Later, it was improvised by a German mathematician, **Leibniz** and the features of multiplication and division were also added to it. Computers came into existence about 150 years later, in the early nineteenth century. A mathematics professor, **Charles Babbage** invented the first generation of computers and then the technology made its way. The growth of computers can be divided into five phases, termed as Generations of Computers. Each

generation is superior from its predecessor in terms of processing, capabilities, appearance, size, switching circuits, and the technologies used. They are:

- First Generation Computers (1940-1956)

- Second Generation Computers (1956-1963)

- Third Generation Computers (1964-1971)

- Fourth Generation Computers (1971-Present)

- Fifth Generation Computers (Present and Ahead)

Figure 1.2 Five Generations of Computer

**(Source-** https://www.inhindis.com/generation-of-computer/)

Let's discuss the five generations of computers in detail.

### 1. The First Generation Computers- Vacuum Tubes (1940-1956)

The first era of computers initiated with an introduction to Vacuum tubes. A vacuum tube is a glass tube filled with certain filaments to generate electricity. It was used to control and increase the intensity of the electronic signals. They served for calculations, storage, and control of the machine. Magnetic drums were used for storage of data, while input was provided through punch cards. The use of machine languages was prominent for programming.

One of the pioneers of this generation was the Electronic Numerical Integrator and Computer (ENIAC) which was developed at the University of Pennsylvania by J. Presper Eckert and John V. Mauchly. It was very large in size, heavy in weight and high in power consumption, approximately, 30-50 feet long and covered the floor area of about 150m<sup>2</sup>, with the weight of 30 tons, the power consumption of nearly 140kW and consisted of more than 18,000 vacuum tubes, 10,000 capacitors, and about 70,000 registers. Interestingly, ENIAC used Decimal representation unlike binary representation of numbers. For example, to represent a digit of a decimal integer, there was a group of 10 vacuum tubes, each signifying a decimal number between zero to nine. Due to enlarged size, large area requirement, a large amount of heat emission, made these computers complex to use. However, they created awareness for the development and further usage of computers.

Another marked contribution was made by **Von Neumann** by designing the Electronic Discrete Variable Automatic Computer (EDVAC) which incorporated memory for both data and the pre-stored programs. Due to rapid access to data and instructions, the operation was much faster and the computer could make logical decisions internally. Later, **Eckert and Mauchly** introduced the first commercially successful computer of this era, the Universal Automatic Computer (UNIVAC), in the year 1952.

# 2. Second Generation Computers- Transistors (1956-1963)

The second generation of computers was based on transistors during the year 1956 to 1963. Transistors were invented in Bell Laboratory in the year 1947 and were used as a replacement for vacuum tubes due to their smaller size and increased efficiency. A Transistor is a device that is composed of semiconductor material that amplifies the signal and can act as a switch (ON and OFF). Along with transistors, other solid-state components like diodes and magnetic core memories instead of magnetic drums for storage of data were used. High-level programming was introduced which used mnemonic codes and symbols. Some of the high-

level languages were FORTRAN (1956), ALGOL (1958), and COBOL (1959).

Digital Equipment Corporation (**DEC**) developed a minicomputer, Programmed Data Processor-1 (**PDP-1**) which was said to be a milestone of this era. It had a display screen of 512 x 512 pixels, a memory of 4096 locations, each location of size 18 bits, speed of 2,00,000 instructions per second. Later, DEC continued with the series with **PDP-8** as an improvised version. Meanwhile, **IBM** also contributed to this generation by the invention of the series of computers, named 700 and 7000. It was observed that the **7094** version of the series by IBM was a 36-bit machine with a memory of 32,536, dominated the market at that time. Apart from this, Control Data Corporation (**CDC**) along with **Cray** encountered more superb inventions **6600** and **7600** of this generation.

# 3. Third Generation Computers- Integrated Circuits (1964-1971)

With the advancement in devices made of transistors, technology took a rapid growth as minimizing the size of transistors and assembling them on a single chip for remarkably increasing the speed and efficiency of computers. A number of transistors along with other components like registers, capacitors, switching devices are assembled on a single chip made of silicon, known as Integrated Circuits (IC). The process of developing the ICs started with small scale integration (SSI). The arrangement tends towards incorporating more components on a single chip, thus changing the process to large scale integration (LSI) and later very large scale integration (VLSI). The invention of ICs proved to be a landmark in the development of computers and other electronic devices of the third generation of computers.

It was first observed by **Gordon Moore** in the year 1965, that every year the number of components (transistors, diodes, etc.) will get double on the single-chip or wafer (silicon base for manufacturing ICs), however, it is noted that the number moderately doubles in approximately every 18 months now. It was predicted that this trend will be followed at least for

a decade, while it is interesting to note that it is still being followed. This is famously known to be **Moore's Law.** In accordance with Moore's law, the miniaturization or shrinking of the size of the components are some highlighted facts for the growth of technology in ICs.

Silicon is chosen to be an elementary and ideal material for designing semiconductor-based devices due to its distinctive properties and ability to be doped with other specific materials (Boron, Arsenic, and Phosphorus) to alter its properties. The standard size of an IC is considered to be less than 0.25 square inches that may have millions of devices integrated on it. The basic mechanics of a computer consists of several ICs mounted on printed circuit boards (PCB) that persist in different functions. There are different ICs for different processes, for example, an IC for memory functioning, another IC for processing of information, etc. Since large circuits were integrated on a single chip, another name given to IC technology was "microelectronics". Due to their small size, the cost of the computers of this generation became low with high processing speed and large memory space. The fast solid-state substituted the core memory of previous-generation memories computers. High- level languages like BASIC (Beginners All-purpose Symbolic Instruction Code) were utilized in this era. The mainframe computer **IBM System/ 360** and the minicomputer **DEC PDP-8** were the important inventions of this generation.

# 4. Fourth Generation Computers (1971- Present)

**VLSI** (Very Large Scale Integration- about 10,000 components per chip) on a single chip, the fourth generation of computers was characterized by the use of Microprocessors, resulting in increased data processing capacity. A microprocessor is an integrated circuit that comprises all the distinct functions of the Central Processing Unit (CPU) of the computer. It is capable of accumulating processing for all arithmetic and logical functions of the computer. For example, the circuit of multiplication of

two numbers can be added to the same chip which is used for switching ON/OFF of the computer. One microprocessor may contain hundreds of integrated circuits or more. When the CPU of the computer is placed on a single chip then the computer is termed as a microcomputer.

This era of computers marked the growth in Microelectronic circuits and digital electronic circuits in different fields. For external storage, floppy disks and magnetic tapes were in use while semiconductor memory chips were considered for main memory. Operating systems like **MS-DOS** and **MS-Windows** were introduced in this generation. Also, the beginning of computer networking through **LAN** and **WAN** was seen by this generation of computers. Another important contribution to this generation was the Graphical User Interface (**GUI**) which developed visual graphics for computer software for the users to make it more attractive and easy to use. It was the time of workstations, personal computers (PC), and microcomputers, which were advantageous in terms of compactness, high speed, low price, user-friendly, fast data processing, less power consumption, and high storage capacity.

Intel 4004 was the first microprocessor chip being developed in this era that included CPU, input/ output control, and memory on a single chip. Other important innovations included Apple II, TRS- Radio Shack, and BBC MICRO. In 1981, IBM collaborated with Intel for an important innovation, IBM PC with Intel 8088 microprocessor. Later, the series of more powerful microprocessors like 80186, 286, 386, 486, Pentium series, and Core 2 Duo processors invaded the market of computers.

# 5. Fifth Generation Computers (Present and Ahead)

The most recent generation of computers is based on Artificial Intelligence and Neural Networks and is still under development. The main aim of the fifth generation of computers is to develop such computers which are self-accessible, self-organizing, learning, and responding to natural languages, ultimately the computers should behave like humans. The voice recognition feature utilized by various

recognized companies like Amazon and Google to develop such devices that can work on just verbal instructions is an example of artificial intelligence technology. Other examples can be seen in online games, education, and intellectual modules for kids and many more fields. However, at present, there is no such computer developed that exhibits artificial intelligence completely but it will soon get into the race. The enhancement in technology has resulted in extremely high speed in the computers. The quantum computers have gained a lot of focus for the future research of technology and developing supercomputers. The technology used for designing such computers will be based on **ULSI** (Ultra Large Scale Integration) and Nanotechnology which is framing a new world of research for miniaturization of the size of the components on a single chip or making way for Nanoelectronics.

Table 1.1 Comparison of five generations of computers

| Generation | Time      | Technology      | Size     | Language    | Speed   | Storage        |

|------------|-----------|-----------------|----------|-------------|---------|----------------|

| / Criteria | Period    |                 |          |             |         |                |

| First      | 1940-     | Vacuum Tubes    | Largest  | Machine     | Slowest | Magnetic       |

| Generation | 1956      |                 |          |             |         | Drums          |

| Second     | 1956-1963 | Transistors     | Large    | Assembly    | Slow    | Magnetic Core  |

| Generation |           |                 |          |             |         | Memories       |

| Third      | 1964-     | Integrated      | Medium   | High- Level | Medium  | Solid State    |

| Generation | 1971      | Circuits        |          |             |         | Memories       |

| Fourth     | 1971-     | Microprocessors | Smaller  | High- Level | Faster  | Semiconductor  |

| Generation | Present   |                 |          |             |         | Memory Chips   |

| Fifth      | Present   | Artificial      | Smallest | High- Level | Fastest | Magnetic RAM   |

| Generation | and Ahead | Intelligence    |          |             |         | or spintronics |

|            |           |                 |          |             |         | based devices, |

|            |           |                 |          |             |         | etc.           |

### 1.6 Operational Concept

The basic need for performing any task on the computer is that there should be a proper list of an instruction set or programming stored in the primary memory. The user makes use of high-level language for writing the instructions or programs which are termed as source codes. The compiler then translates the high- level source code into machine language code that is stored in the memory. The CPU fetches these instructions from the memory and executes them and then again sends the processed data to be stored in the memory. If there are many instructions that are to be executed concurrently, then the CPU works in a multiplexed form. The basic operational concept explains how the execution of the instructions is carried out by the CPU. This includes several parameters and steps that are being discussed one by one.

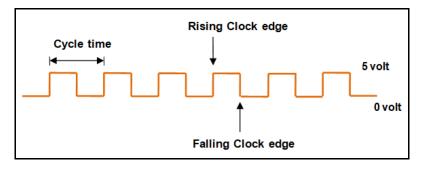

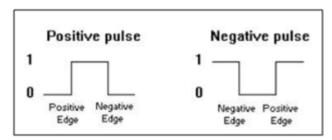

• **Processor Clock:** The clock is the main parameter of any process that depicts the proper timing of the process. It is a digital clock that produces ON and OFF states at regular time intervals. Figure 1.5 shows the oscillating cycle representing the range from 0-5 volts with a cycle time of one pulse. Here, we can see two different edges of the clock signal i.e. rising clock edge and falling clock edge, also known as positive edge and negative edge respectively, displaying the transition of the clock for increment or decrement of the program counter. For reference, if the clock speed of any processor in any electronic device is given as 4 GHz, then the cycle time for one process can be calculated by 1/ clock speed, which shows how fast the processor can execute one operation. To execute any instruction, the process of operation is divided into a sequence of steps that can be completed in one clock cycle each. Today, such processors are available in the market having the speed range of a hundred million cycles to over a billion cycles per second.

Figure 1.5 Processor Clock cycle

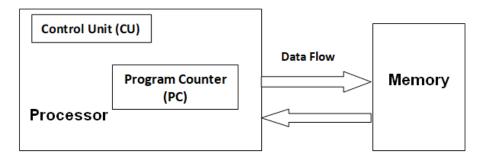

• **Program Counter (PC):** The processor comprises a binary/ digital counter called program counter that gets incremented by one on every cycle of the clock signal. It is a register that consists of a group of bits and contains the address of the next instruction to be accomplished from the memory. A register can be considered to be the smallest storage unit in the processor that can hold an instruction, memory address, or any other bit sequence. The data when entered by the user gets stored in the main memory of the computer then it is fetched by the CPU, so the program counter keeps the count of these instructions and gets updated when the execution of one instruction is over.

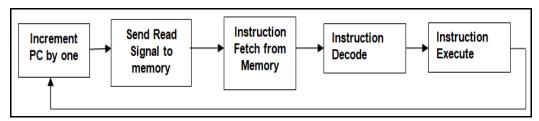

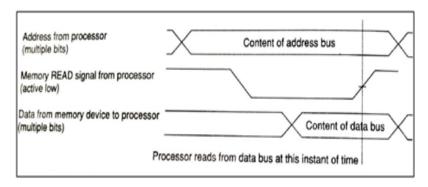

Figure 1.6 Reading Data from Memory

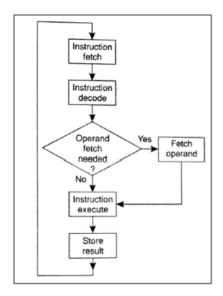

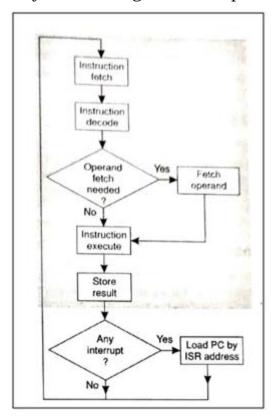

- **Instruction Fetch:** The process of fetching the data to be executed by the CPU in the form of instruction is known as instruction fetch. As soon as the instruction is fetched, the information of this instruction byte gets available in the processor. With the next clock cycle, the program counter is incremented by one and waits for the next instruction fetch process to be completed.

- **Instruction Decode:** As soon as the processor reads the instruction byte of the fetched instruction, it starts understanding it; this process is called Instruction Decoding. An increased number of instructions makes the decoding process complex. There are certain techniques to reduce this complexity which we will discuss in upcoming units.

- **Instruction Execute:** After the decoding of the instruction, the execution of the instruction is started by the processor immediately.

Thus, the process of incrementing the PC, fetching, decoding, and executing the instruction continues. In earlier processors, all these steps occupied different time slots and resulted in the slow speed of the processor, but with modern processors, the issue was solved by accomplishing the whole process simultaneously. This is called Pipelining.

Figure 1.7 Basic Operational Flow of a processor

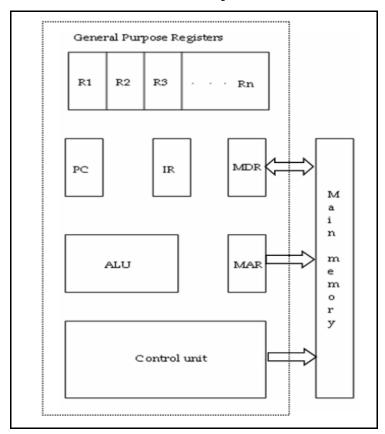

Besides the Program counter (PC), there are several other registers in the processor that are used for different purposes. Some are used to establish the connection between the memory and the processor while some are used for fetching instructions from the memory for execution. They are:

- **Instruction Register (IR):** It is a register that contains the instruction that is presently under execution.

- **General Purpose Registers:** There are n- general-purpose registers ranging from  $R_0$  to  $R_{n-1}$  which are used to store data generally when required.

- **Memory Address Register (MAR):** It holds the address of the location in the memory that is to be accessed.

- **Memory Data Register (MDR):** It includes the data that is to be read or written into, out of the memory address.

The complete steps for operation flow are:

- 1. Initially, the set of instructions called a program is either in the memory itself or usually received through Input from the user.

- 2. The Program Counter (PC) points at the first instruction of the program and the execution starts.

- 3. The instruction from the PC is transferred to **MAR** and it sends a 'Read' signal to the memory as shown in figure 1.7.

- 4. When the memory access time gets over, the address is read out of the memory and transferred into **MDR**.

- 5. The contents of MDR are now loaded into **IR** and the instruction gets ready to be decoded and executed. After the execution of an instruction, the address of the location where the result is stored is sent to MAR.

- 6. Then the PC gets incremented by one to indicate that it is ready for the next instruction to be executed.

### 1.7 Summary

- According to the Von Neumann architecture, one can encode and even store the instructions in the memory of the computer so that they can be executed whenever required. The only issue with this architecture was that only one instruction was being fetched at a time, or the memory could be accessed only once a while.

- The evolution of the computer system in five generations depicts the enhancement in quality, efficiency, accuracy, storage capacity, and speed of computers.

- The building blocks of a computer include both hardware and software components. The motherboard or processor is the heart of the computer.

The operating system is known as the interface between a user and computer, different programs and languages form the software building blocks of the system.

- The program counter is a register that contains the information of the next instruction to be executed. Besides PC, instruction register (IR), Memory Address Register (MAR), Memory Data Register (MDR), and general-purpose registers are other registers that are used in the basic operational concept of computers.

- The program counter is a register that contains the information of the next instruction to be executed. Besides PC, instruction register (IR),

Memory Address Register (MAR), Memory Data Register (MDR), and general-purpose registers are other registers that are used in the basic operational concept of computers.

### 1.8 Key Terms

- **SRAM:** Static Random Access Memory is a semiconductor that holds the data in a static manner and does not change rapidly but it is volatile in nature.

- **DRAM:** Dynamic Random Access Memory is a type of semiconductor memory that stores each bit of data in a separate capacitor. The storage is dynamic i.e. the content can be changed whenever required. It can store more data than SRAM but requires more power.

- **PROM:** It is a programmable read-only memory that can be programmed once by the user according to the need and the data remains permanent in PROM. It is a non-volatile memory.

- **EPROM:** Erasable programmable read-only memory is a type of ROM that can be erased and reused, unlike PROM. The memory is erased using UV-rays. The EPROM chip has to be removed from the system and then erased and reprogrammed.

- **EEPROM:** Electrically erasable programmable read-only memory can be erased and reprogrammed repeatedly by applying a higher voltage pulse. There is no need to remove the chip each time, it is user-modifiable. It is also termed as an upgraded version of EPROM.

# 1.9 Check Your Progress

- Q1) Explain the purpose of the Program Counter.

- Q2) Write a short note on General-purpose registers in the computer system.

- Q3) Discuss the classification of Memory in detail.

- Q4) Explain the basic operational function of the computer system.

- Q5) Describe the generations of computers in detail.

- Q6) What is the advantage of Harvard Architecture?

Q7) Define Von Neumann architecture of computers with its drawbacks.

### References:

Computer System Architecture, M. Morris Mano

Computer Architecture and Organization, Subrata Ghoshal, Pearson Publication

http://www.egyankosh.ac.in/bitstream/123456789/10950/1/Unit-1.pdf

https://www.academia.edu/35443462/Computer\_Generations

http://www.idconline.com/technical\_references/pdfs/information\_technology/

$Basic\_Operational\_Concepts\_of\_Computer.pdf$

https://www.researchgate.net/publication/336700280\_History\_of\_computer\_a

nd\_its\_generations

https://www.geeksforgeeks.org/computer-organization-von-neumann-

architecture/

# Unit 2 - Digital Logic Circuits

### Structure

- 2.0 Introduction

- 2.1 Unit Objectives

- 2.2 Boolean Algebra

- 2.2.1 Boolean Operators 2.2.2 Truth Table

- 2.2.3 Boolean Identities

- 2.3 Logic Gates

- 2.3.1 Common Logic Gates 2.3.2 Universal Gates

- 2.3.3 Combinational Gates

- 2.4 Map Simplification

- 2.5 Combinational Circuits

- 2.5.1 Decoder 2.5.2 Multiplexer

- 2.6 Arithmetic Circuits

- 2.7 Sequential Circuits

- 2.7.1 Basic Latch 2.7.2 Flip- Flop

- 2.8 Registers and Counters

- 2.9 Summary

- 2.10 Key Terms

- 2.11 Check Your Progress

### 2.0 Introduction

Digital Logics form the fundamentals of the computer system. The computer works on the binary logic of '0' and '1' bit that is considered as the smallest unit. All the arithmetic and logical operations and others are performed on the basis of binary systems and the digital circuits. The computer accepts the data from the user in a user-friendly language and then the data is converted into machine codes in binary form. After execution, the result is again converted to the language understandable by the user.

Following are the units of a binary system that are used in computers:

- **Bit:** 0 and 1

- **Nibble:** Group of 4 bits.

- **Byte:** Pair of 2 nibbles or 8 bits.

- **Word:** Group of 2 bytes or 16 bits.

- **Double Word:** Combination of 2 words or 32 bits.

- **Quad/ Long Word:** Group of 2 double words or 64 bits and so on.

The basic function of a computer is governed by either sequential or combinational circuits using digital logic. There are two basic modules of data processing and control operation, data storage and data flow control. These modules are implemented by circuits based on digital logic using flip- flops or logic gates that are said to be the fundamentals of digital circuits. The operation is performed in such circuits using the mathematical foundation called Boolean algebra that helps in analyzing and designing the circuits. In this unit, we are going to discuss all these logical circuits in detail.

# 2.1 Unit Objectives

After completion of this unit, the reader will be able to:

- Understand the basics of Boolean algebra and Logic gates.

- Analyze combinational, arithmetic, and sequential circuits.

- Study the basics of registers, counters, and memory circuits.

# 2.2 Boolean algebra

Boolean algebra is the mathematical foundation that is used to design the digital circuitry and other digital systems and analyze their behavior and fundamentals. **George Boole**, an English mathematician proposed the basics of Boolean algebra in 1854. Later, in 1938, **Claude Shannon** suggested that this algebra can be used in designing switching circuits in the digital electronics field. The field of computer architecture and organization is concerned with digital electronics due to two major functions to be implemented. They are storing Boolean information, which is implemented

using registers and flip-flops, and transferring this Boolean information from one place to another with the help of logic gates. The simplest analogy of Boolean algebra is a switch that has two states ON and OFF representing logic 1 (True or positive) and logic 0 (False or negative) respectively. Certain variables and operators are used in Boolean algebra that is termed as Boolean operators.

# 2.2.1 Boolean Operators

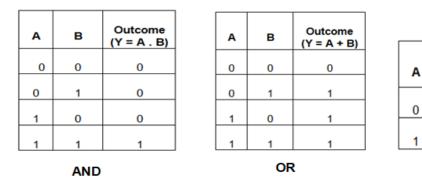

The basic logical operations include AND, OR, and NOT, generally represented as '.', '+', and '-' (an over-bar sign on the variable) respectively. Let us assume that A and B are two variables both having two states (0 and 1), then

A AND B = A.B A OR B = A + B NOT A = Ā

- **AND operator:** The operation AND is true only if both the variables A & B are true. That means if we consider the example of a switch, both A & B are two switches. When both A & B are closed (on) or open (off) then only the AND operation will give true outcome. If anyone of them is on and others are off then the outcome will be false.

- **OR operator:** This operation is true if both A & B are in different states. If either or both A & B switches are closed (on) then only the outcome of the operation will be true.

- **NOT operator:** It is the simplest operator as it represents the inverse of the original state. The outcome of NOT for logic 0 (false) is 1 (true) and for logic 1 (true) is 0 (false).

#### 2.2.2 Truth Table

A truth table is a representation of Boolean operators in a tabular form. It becomes easy to understand the Boolean expressions with the help of truth tables. It represents OFF state as 0 and ON state as 1. Figure 2.1 shows the truth table of AND, OR and NOT operators.

Figure 2.1 Truth tables of AND, OR, and NOT operators

Outcome

$(Y = \bar{A})$

0

NOT

#### 2.2.3 Boolean Identities

To simplify and solve the different functions of Boolean algebra, there are several identities available. These are some basic rules that are followed in Boolean algebra to solve the Boolean expressions. Table 2.1 shows the different Boolean identities, considering the Boolean operators and variables.

Table 2.1 Fundamental Boolean Identities

| Identities (AND form)                          | Identities (OR form)                         | Name               |

|------------------------------------------------|----------------------------------------------|--------------------|

| 1.A = A                                        | 0+A = A                                      | Identity Law       |

| 0.A = 0                                        | 1+A = 1                                      | Null Law           |

| $A.\bar{A}=0$                                  | A+Ā = 1                                      | Inverse Law        |

| A.B = B.A                                      | A+B = B+A                                    | Commutative Law    |

| A.A = A                                        | A+A = A                                      | Idempotent Law     |

| A.(B.C) = (A.B).C                              | A+(B+C) = (A+B)+C                            | Associative Law    |

| A.(B+C) = (A.B)+(A.C)                          | A+(B.C) = (A+B).(A+C)                        | Distributive Law   |

| A.(A+B) = A                                    | A+A.B = A                                    | Absorption Law     |

| $\overline{A.B} = \overline{A} + \overline{B}$ | $\overline{A+B} = \overline{A}.\overline{B}$ | DeMorgan's Theorem |

#### 2.3 Logic Gates

Logic gates are said to be basic components in the field of digital electronics. They are used to generate simple to complex digital circuits. It can have one or more variables as input depending upon the number of signals and generate

one result after performing logical operations between the inputs. These logic gates accept binary inputs 0 (False/ OFF) and 1 (True/ ON) and perform the desired operations on such signals. They are generally designed with the help of electronic switches such as diodes and transistors. With the help of logic gates, Boolean expressions can also be implemented in electronic circuitry. Gates are categorized as **Primary Gates** (AND, OR, and NOT), **Secondary/Derived Gates** (NAND, NOR- known as Universal gates and XOR, XNOR-known as Combinational gates). The symbol and representation of these logic gates are prescribed by ANSI/ IEEE standards. Let us discuss them in detail.

# 2.3.1 Common Logic Gates

We will discuss the common or primary logic gates one by one.

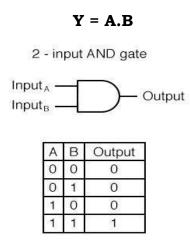

• **AND Gate:** There are two or more input signals in AND gate. The output of AND gate is TRUE only if all input variables are TRUE otherwise the output is FALSE. It performs logical multiplication i.e. AND function. As now we are considering only 2 input variables, so the truth table will have  $2^2 = 4$  combinations at the input side. To generalize, the input combinations in the truth table are dependent on the 'n' number of input signals as  $2^n$ .

Figure 2.2 Symbol and Truth Table of AND gate

(Source- https://www.allaboutcircuits.com/textbook/digital/chpt-3/multiple-input-gates/)

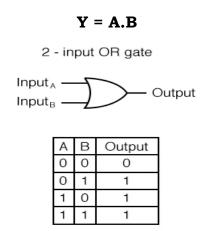

• **OR Gate:** In an OR gate, the number of input signals can be two or more and output is only one, just like in And gate. The output is TRUE if any of the input is TRUE otherwise it is FALSE. Logical addition is performed i.e. OR function.

Figure 2.3 Symbol and Truth Table of OR gate

**(Source-** https://www.allaboutcircuits.com/textbook/digital/chpt-3/multiple-input-gates/)

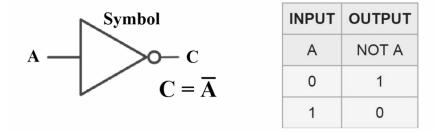

• **NOT gate:** It is one input and one output logical gate that gives the inverse outcome of the input. It performs inversion or complementation of the given input signal i.e. if the input is TRUE the outcome of NOT fate will be FALSE and vice versa.

Figure 2.4 Symbol and Truth Table of NOT gate

**(Source-** https://projectiot123.com/2019/05/24/introduction-to-not-gate/)

# 2.3.2 Universal Gates

Both NAND and NOR logical gates are termed as universal logic gates. It is due to the fact that all other logic gates can be accomplished by using either of these two gates. Let's discuss them with their symbolic representation and truth table.

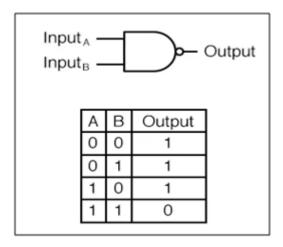

• **NAND gate:** It is designed by combining AND gate and NOT gate. As it is the inverse of AND gate, so the output of the NAND gate is FALSE when all inputs are TRUE otherwise it is TRUE.

Figure 2.5 Symbol and Truth Table of NAND gate

(Source- https://www.allaboutcircuits.com/textbook/digital/chpt-3/ttl-nand-and-gates/)

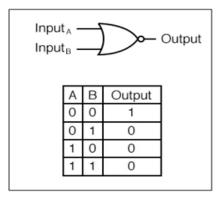

• **NOR gate:** It is accomplished by the combination of OR and NOT gate. It provides the output as TRUE only when both the input signals are FALSE, otherwise, the output is FALSE. It generates a complement of the OR gate.

Figure 2.6 Symbol and Truth Table of NAND gate

(Source- https://www.allaboutcircuits.com/textbook/digital/chpt-3/ttl-nor-and-or-gates/)

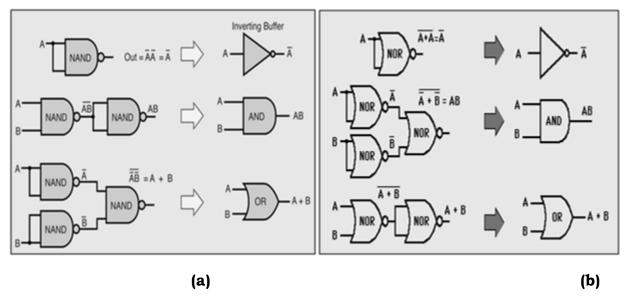

As it is already discovered that NAND and NOR gates are universal gates as they are the simplest logic gates to combine and generate all other basic gates. Figure 2.7 (a) & (b) shows how the basic gates are accomplished using these universal gates.

Figure 2.7 Generating other gates from NAND and NOR gates

**(Source-** http://hyperphysics.phy-astr.gsu.edu/hbase/Electronic.html)

#### 2.3.3 Combinational Gates

The combinational gates are designed by combining the common (AND, OR, and NOT) and universal gates (NAND and NOR). There are two combinational gates Exclusive OR (XOR) and Exclusive NOR (XNOR).

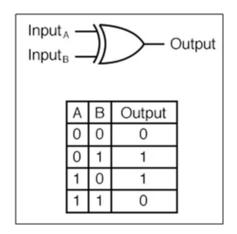

• **XOR Gate**: It is also called the Exclusive OR gate. The output of the XOR gate is TRUE when either of the two inputs is TRUE, otherwise, it is FALSE. Generally, it is a 2 input and 1 output gate but when required it can be used for multiple inputs, such as multiple XOR gates that can be used in combination. The output of such multiple XOR gate will depend on the number of TRUE outcomes, the result will be '1' when the number of 1s in the input is even.

Figure 2.8 Symbol and Truth Table of XOR gate

(Source- https://www.allaboutcircuits.com/textbook/digital/chpt-3/multiple-input-gates/)

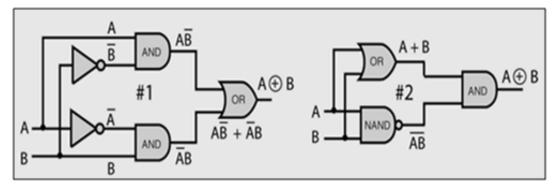

The XOR gate can also be designed using the basic gates. Figure 2.9 illustrates the equivalent circuit of the XOR gate using AND, OR, and NAND gate in two ways:

- 1.  $A \oplus B = AB + B\overline{A}$

- 2.  $A \oplus B = (A+B) (AB)$

Figure 2.9 Equivalent circuit of XOR using other logical gates

**(Source-** http://hyperphysics.phy-astr.gsu.edu/hbase/Electronic/xor.html)

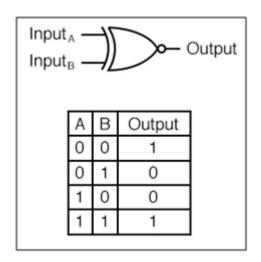

• **XNOR Gate:** The Exclusive NOR (XNOR) gate can be accomplished with the help of XOR followed by NOT gate. The output of XNOR is TRUE when the input signals are the same and FALSE when the inputs are different.

Figure 2.10 Symbol and Truth Table of XNOR gate

**(Source-** https://www.allaboutcircuits.com/textbook/digital/chpt-3/multiple-input-gates/)

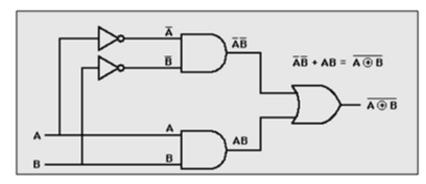

Like the XOR gate, the XNOR gate can also be designed using basic gates, as shown in figure 2.11.

Figure 2.11 Equivalent circuit of XNOR using basic gates

(Source- http://hyperphysics.phy-astr.gsu.edu/hbase/Electronic/xnor.html)

#### 2.4 K-Map Simplification

As the internal circuitry of the computer system is based on the Boolean algebra but it is much more complex to implement and execute. Complex logic diagrams and Boolean functions are the results of complex algebraic expressions of the circuits. The functionality of the algebraic functions may differ as they appear. The truth table is a unique feature for every function.

A simple approach to simplify these Boolean expressions is the Map Simplification method. It is the procedure of representing the truth table in a pictorial form and selecting the minimum terms required to express a particular Boolean function. Another name for the map method is **Karnaugh map or K-map**. Due to this minimization in the number of terms, there will be less number of logic gates and lesser number of variables in a Boolean expression. This will also ultimately result in reduced cost and power consumption of the computer system.

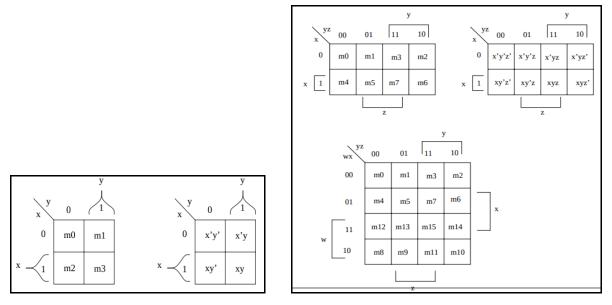

Figure 2.12 K-map for 2,3, and 4 variables

(Source- http://osp.mans.edu.eg/cs212/CS212\_chapter\_3\_notes.pdf)

After simplification of a Boolean function using K-map, the obtained result is in a specified form. There are two fundamental forms of a logic function. A logical expression can occur as 'Sum of Products (SOP)' or 'Product of Sums (POS)'. SOP and POS are complementary to each other.

• Sum of products (SOP) simplification: In this form, the sum terms perform the OR operation and the product refers to the AND operation of these terms. It will be clearer with the help of an example. Let us consider the truth table for 3 input variables A, B & C generating the output Y=1 when the variables are ANDed for the condition of rows 2,3,5,7. In any of the four cases, the output will be 1, so as a cumulative result, these conditions can be ORed.

| Row | A | В | С | Y |

|-----|---|---|---|---|

| 1   | 0 | 0 | 0 | 0 |

| 2   | 0 | 0 | 1 | 1 |

| 3   | 0 | 1 | 0 | 1 |

| 4   | 0 | 1 | 1 | 0 |

| 5   | 1 | 0 | 0 | 1 |

| 6   | 1 | 0 | 1 | 0 |

| 7   | 1 | 1 | 0 | 1 |

| 8   | 1 | 1 | 1 | 0 |

Then the required equation will be,

$$Y = \overline{A} \overline{B} C + \overline{A} B \overline{C} + A \overline{B} \overline{C} + A B \overline{C}$$

Each term in the above equation corresponds to minterms and is expressed using the symbol  $\sum m$ .

• **Product of Sums (POS) Simplification:** In this form, the product terms perform the AND operation and the sum refers to the OR operation of these terms. Each term in POS form is referred to as maxterm and is denoted as **IIM.** For example,

Some Major features of K-Map are:

• In the SOP form, the combination of variables is called a minterm, which is represented in a truth table. The K-map is equipped with a possible minterm in each cell. For example, the truth table of the Boolean expression shown in figure 2.10 for the XOR gate contains four minterms. Generally, if a Boolean function is expressed by using n variables it will have  $2^n$  minterms. The information in a truth table can be compacted by only listing the minterms that give the output '1'. For example, in figure 2.10, the Boolean expression for the XOR gate can be expressed as:

$$F(A, B) = \sum m(0, 4)$$

The minterms (0, 4) refer to the binary variables of the truth table of XOR gate. The symbol  $\sum$  denotes the sum of the minterms. The minterms which are not included in the above equation represent that the output of such variables are '0'.

- The K-map consists of squares, each square represents one minterm. The minterms with output '1' are marked as '1' and others are marked as '0' or left empty. Various combinations and patterns of the squares marked as '1' are generated and they result in alternative algebraic expressions for the given Boolean function.

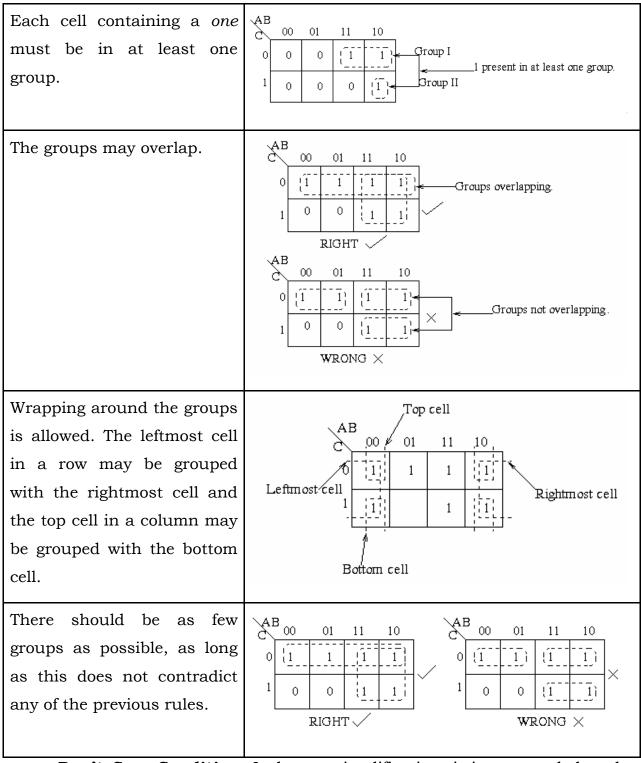

- **Grouping:** If there are two adjacent 1's in the squares of K-map then grouping can be done to simplify the equation. Similarly, four 1's can also be grouped. To generalize, 1's can be grouped only in multiples of 2. Another grouping can be done for the corners, if there are 1's in every corner then, a group can be formed by rolling up the lower 1's and forming the group of four 1's. The priority of grouping can be set accordingly to cover the maximum number of 1's in the map. Table 2.2 shows the grouping rules for K-map simplification.

Table 2.2 Rules for grouping in k-map simplification

| Rules                                                                                                                                                                      | Example                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Groups may not include any cell containing a zero                                                                                                                          | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                 |

| Groups cannot be diagonal, can be vertical or horizontal.                                                                                                                  | WRONG X  B  0  0  0  1  1  1  1  1  1  1  1  1  1                                                                                     |

| A group can only be formed for $2^n$ cells, $n=1, 2, 3$ . If $n=1$ , a group will contain two 1's since $2^1=2$ . If $n=2$ , a group will contain four 1's since $2^2=4$ . | AB 0 1 Group of 2 0 0 1 11 10 Group of 3  1 0 0 WRONG X  AB 00 01 11 10 Group of 3  WRONG X  AB 00 01 11 10 Group of 5  1 1 1 1 1 1 1 |

| A group should be as large as possible to cover up maximum cells.                                                                                                          | AB 00 01 11 10 0 11 10 0 11 10 0 11 10 0 11 10 0 0 11 11                                                                              |

• **Don't Care Condition:** In k-map simplification, it is assumed that the cells which do not have output as 1 can be marked as 0. But, there are certain cases in which there are no combinations of the input variables. In such a situation, these cells can be marked as 0 or 1. Such conditions

are referred to as *don't care conditions* and denoted as 'x'. They can be considered as 0 or 1 according to the requirement to form the proper groups in the k-map.

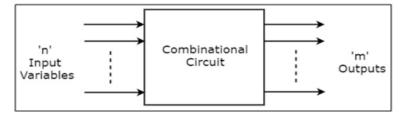

#### 2.5 Combinational Circuits

In the above section, we have studied logic gates which form the basis of various types of circuits in digital electronics. The combinational circuits are formed by the combination of basic and other gates. The output of combinational circuits depends upon the combination of inputs and does not change dynamically due to some clock input. These circuits have 'm' outputs for 'n' input signals as shown in figure 2.12. Some combinational circuits are represented in figure 2.7 (a) & (b) where universal gates NAND and NOR are used to generate the basic gates. Decoder and Multiplexer are other examples of the combinational circuits.

Figure 2.12 Combinational Circuit with n inputs and m outputs

(Source- ttps://www.tutorialspoint.com/digital\_circuits/digital\_combinational\_circuits.htm)

To design a combinational circuit, the following procedure is followed:

- 1. The given specifications decide the number of inputs and outputs.

- 2. Generate **Truth Table**. For 'n' inputs '2<sup>n</sup>' combinations are possible. With the help of the truth table, output for corresponding input can be obtained.

- 3. **Boolean expression** is generated for each output and it is simplified.

- 4. Using **logic gates**, the simplified Boolean expression is implemented in a circuit form.

- Decoder

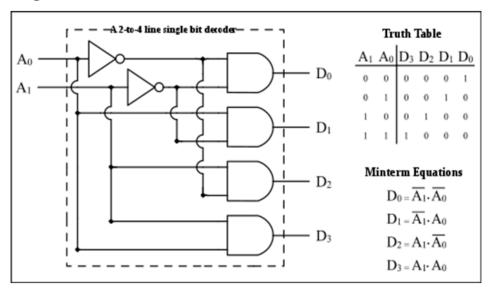

While transmitting any information, the data is encoded into certain codes and at the receiver's end; it is decoded to be understandable by the receiver. A decoder is a device that is used to decode the codes at the receiver end. The basic circuit of a decoder is obtained from combinational circuits, having 'n' input lines, and '2n' output lines. Whenever the decoder is enabled, it will select one output for the combination of inputs i.e. it detects a particular signal.

The binary decoders of type 'n to 2n' are the combinational circuits that modify the binary data from 'n' coded inputs to '2n' outputs. For example, 2 to 4 line decoder, 3 to 8 line decoder, or 4 to 16 line decoder. Figure 2.13 shows the simplest 2 to 4 decoder with 2 input lines A<sub>0</sub> and A<sub>1</sub>, and 4 outputs drawn with the combination of the inputs D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, and D<sub>3</sub>. The truth table for the decoder indicates that if either both or any input is high (1) then the decoder will generate one output at a time. The minterm equations indicate Boolean expression for each input combination and the equivalent circuit represents the use of AND gate and NOT gate to form a decoder.

Figure 2.13 Truth table, Boolean expressions, and Equivalent Circuit for 2 to 4 decoder

(Source- https://en.wikipedia.org/wiki/File:Decoder\_Example.svg)

# Multiplexer

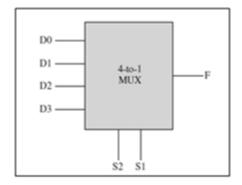

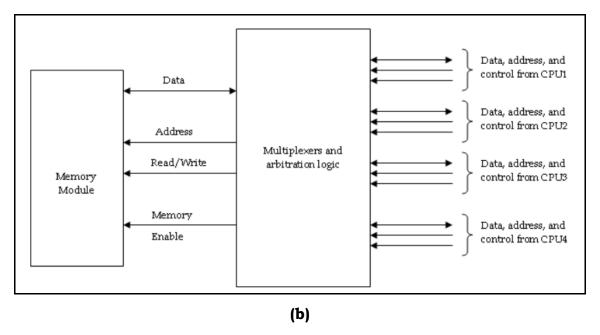

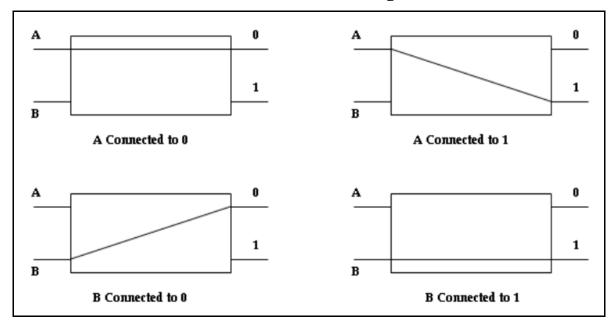

A multiplexer is a switching combinational circuit being widely used in the field of digital electronics. It is a multiple-input and only one output device, generally used as a data selector. It is memory-less and no feedback path is observed in a multiplexer. A MUX (short term for Multiplexer) can be constructed using either traditional transistors like MOSFETs and relay switches or using high-speed logic gates to switch the voltage and binary data as input respectively through a single output. Generally, a multiplexer has '2n' input lines and 'n' select/ control lines and one undistorted output. The select lines help in selecting the particular input at a time. Combinations of input signals and select lines are formed and with the help of truth table and Boolean expressions, we are able to generate the equivalent circuit of the multiplexer using required logic gates. In the field of Computer architecture, the multiplexer is very important in data communications through the buses.

Figure 2.14 represents the basic 4-to-1 Multiplexer having 4 inputs D0, D1, D2, and D3, F is the output, and S1 and S2 are select lines. The circuit is obtained by using basic logic gates. NAND and NOR gates can also be used to determine the circuit of a multiplexer. Here, we can see that every select line whether 'high' or 'low' gives an input combination as the output. Besides this, we can also construct 8-to-1, 16-to-1 multiplexers, and so on.

| S2 | S1 | F  |

|----|----|----|

| 0  | 0  | D0 |

| 0  | 1  | D1 |

| 1  | 0  | D2 |

| 1  | 1  | D3 |

Figure 2.14 4-to1 Multiplexer block diagram, truth table, and circuit diagram

(**Source-** Computer Organization and Architecture, Ninth Edition, William Stallings, Chapter-11, Page no. 380)

#### 2.6 Arithmetic Circuits

The circuits that are capable of performing arithmetic operations in any digital system are called Arithmetic Circuits. They are also sort of combinational circuits. The primary operation is addition, which forms the basis for other arithmetic operations like subtraction, division, and multiplication. All these operations will be discussed in upcoming units; here we are going to discuss the adder circuits in the digital system.

The binary addition is different from the Boolean algebra. We all are aware of the fact that the basic mathematical addition generates a 'carry' after performing the operation. Similarly, in binary addition also, a carry is generated but it is not so in case of Boolean algebra. The basic rules for binary addition are:

- 0+0=0

- 0+1=1

- 1+0=1

- 1+1 = 0 and carry 1 (the binary number 10)

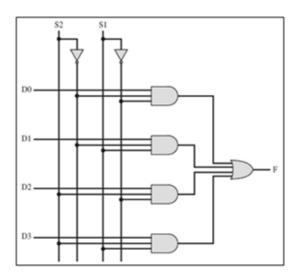

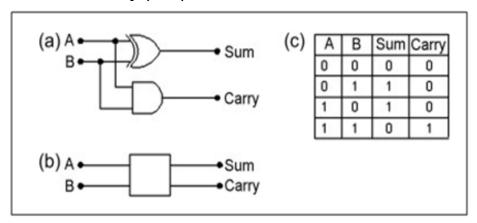

There are two basic addition circuits developed in the binary system, Half-adder and Full- adder. Let's have a look at the specifications of both circuits.

#### • Half- Adder

It is the simplest adder circuit of a binary system that allows the addition of two bits, generating the output sum and a carry bit. The half-adder circuit is constructed by combining an **XOR** and an **AND** gate. The carry bit is '1' only when both the bits are '1' otherwise; it is '0', as shown in figure 2.15.

The Boolean expression for half-adder can be:

Sum =  $A \oplus B$  and Carry ( $C_{out}$ ) = A.B

Figure 2.15 Half- adder circuit, block diagram, and truth table (Source- https://www.sciencedirect.com/topics/engineering/arithmetic-circuit)

#### • Full- Adder

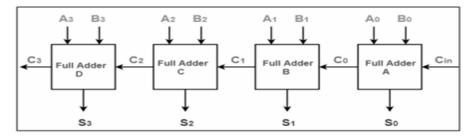

In a binary system, half-adder is sufficient to add two bits and it also produces a carry-out. But if the addition of more than two bits is to be considered, then the carry generated can't be ignored. The full- adder generates carry out and simultaneously uses this carry again as an input. That means, in a full-adder circuit, there are three input signals, two of them are operands to be added and the third input signal is the Carry  $(C_{in})$ .

The full-adder circuit can be constructed by combining two half-adder circuits with the help of an OR gate. Figure 2.16 represents the circuit

diagram and truth table for full-adder. The Boolean expression for full-adder can be denoted as:

$$\begin{aligned} \mathbf{Sum} &= \mathbf{A} \oplus \mathbf{B} \oplus \mathbf{C}_{in} \\ \mathbf{C}_{out} &= \mathbf{A} \cdot \mathbf{B} + (\mathbf{A} \oplus \mathbf{B}) \cdot \mathbf{C}_{in} \\ \mathbf{C}_{out} &= \mathbf{A} \cdot \mathbf{B} + (\mathbf{A} + \mathbf{B}) \cdot \mathbf{C}_{in} \\ \end{aligned}$$

Figure 2.16 Full- adder circuit, block diagram, and truth table (Source- https://link.springer.com/chapter/10.1007/978-3-030-13605-5\_12)

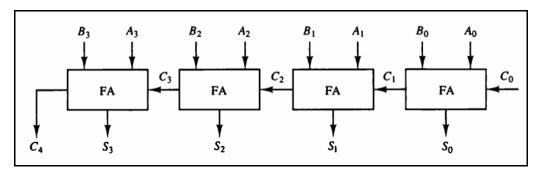

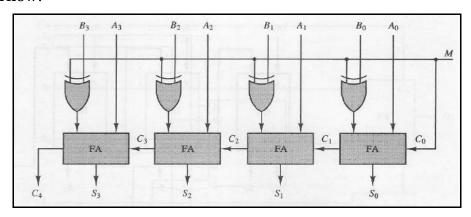

It is also a fact that a full-adder can be converted to a half-adder circuit if the carry input C<sub>in</sub> is connected to a 0 voltage level permanently. To design an n-bit adder, full- adders can be cascaded together in such a way that carry is forwarded from full-adder A to full-adder B and sum is generated on each full-adder circuit but it is dependent on the carry bit from the previous circuit, as shown in figure 2.17. It is also known as Ripple Carry Adder.

Figure 2.16 Block diagram of 4-bit adder using full-adders in cascaded form

# 2.7 Sequential Circuits

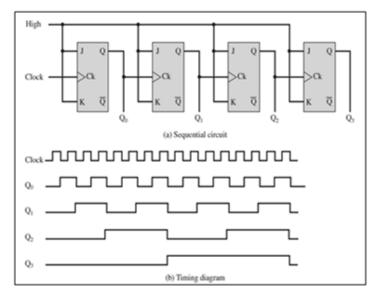

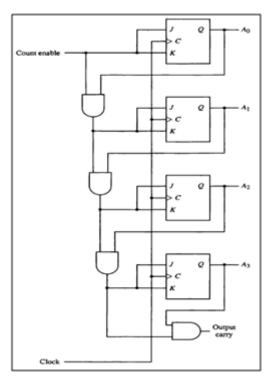

The sequential circuits are dynamic in nature i.e. the output of such digital circuits is time-dependent and changes with time. They are used to provide a memory to the binary operations in the digital system. They are more complex circuits than the combinational circuits. The output of the sequential circuits is dependent on the current as well as previous inputs. These circuits follow the concept of feedback and are said to be operated by a *clock signal* that is generated using a *clock generator circuit*. The clock pulse operates between 0 and 1 level. The circuit operates when the clock is at level 1. The clock signal plays an important role in sequential circuits to make them operate in *Sunchronous* mode.

Figure 2.17 Clock Pulse

(**Source-** http://www.circuitstoday.com/triggering-of-flip-flops)

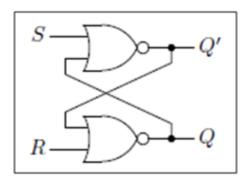

#### 2.7.1 Basic Latch

A latch is a storage device with the capacity to store one bit at a time. It can be constructed using two or more logic gates such that the output of one gate can be fed as input to the other and the output of this second gate can be given as feedback input to the first gate. Figure 2.18 represents the NOR gate circuit

implementation for the most fundamental latch i.e. **SR- Latch** (Set- Reset). The circuit has two inputs S (Set) and R (Reset), two outputs Q and Q'. The fact can be noted that the latch can remain in the same state until the next input is given to it, i.e. it can store the data till the next input. If Q = 1 (Q = 0), then the latch is *Set*, while if Q = 0 (Q = 1), then it is *Reset*. The circuit is said to be *bistable* as it has two stable states.

| Inputs |   | Outputs |     |

|--------|---|---------|-----|

| s      | R | Q       | Q'  |

| 0      | 0 | $Q_0$   | Q'o |

| 1      | 0 | 0       | 1   |

| 0      | 1 | 1       | 0   |

| 1      | 1 | X       | X   |

Figure 2.18 Implementation of SR- Latch by using NOR gate and its truth table

(Source- Introduction to Computer Organization, Robert G. Plantz, Chapter- 5, Page no. 96)

The operation of SR- Latch is followed as four possible input combinations:

# a) S = 0, R = 0 (Keep Current State)

• If Q = 0 and Q' = 1, then the output of the upper NOR gate is 1 and that of lower NOR gate is 0.

• If Q = 1 and Q = 0, the output of the upper NOR gate is 0 and that of lower NOR gate is 1.

Thus, the state is maintained as SET or RESET, due to the cross feedback between both the gates.

# b) S = 1, R = 0 (Set)

- If Q = 1 and Q = 0, the upper NOR gate gives the output 0 and the lower NOR gate gives 1. This means that the latch is in *Set* state.

- If Q = 0 and Q = 1, the upper NOR gate will give the output 0, which is given back to the lower NOR gate to produce the output as 1. This cross-feedback system maintains the output of the upper NOR gate at 0.

## c) S = 0, R = 1 (Reset)

- If Q = 1 and Q= 0, the lower NOR gate will produce the output of 0, therefore causing the upper NOR gate to produce the output as 1. The latch moves into the *Reset* state.

- If Q = 0 and Q = 1, the output of the lower NOR gate is 0 and that of the upper NOR gate is 1. Thus, the latch remains in the Reset state only.

## d) S = 1, R = 1 (Undefined state)

- If Q = 0 and Q' = 1, the output of the upper NOR gate (0) is given back as an input to the lower NOR gate, giving the output as 0. Thus, the condition appears when Q = Q' = 0, which is an undefined state.

- If Q = 1 and Q' = 0, the output of the lower NOR gate (0) is given as an input to the upper NOR gate to give output 0. Again the same condition appears Q = Q' = 0, which is an undefined state.

# 2.7.2 Flip- Flop

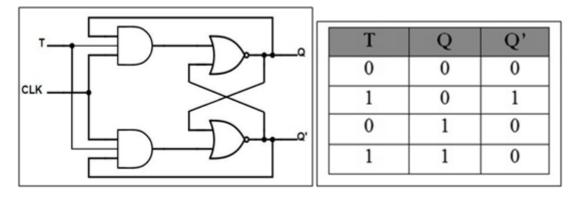

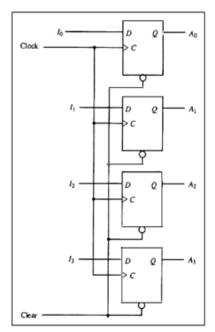

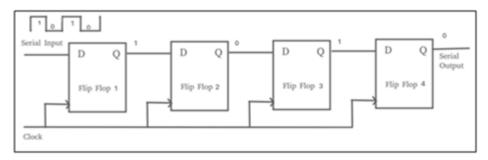

A flip- flop is the combination of latches and changes its output with the clock pulse to provide synchronous output. It has 1-bit memory like a latch. The difference between a latch and a flip-flop is in terms of a clock signal. Flip- flop is regulated according to the clock pulse and it produces synchronous output, while latch doesn't depend on the clock pulse. We will now discuss the different

types of flip-flops that are most widely used in the digital circuits and in computer hardware.

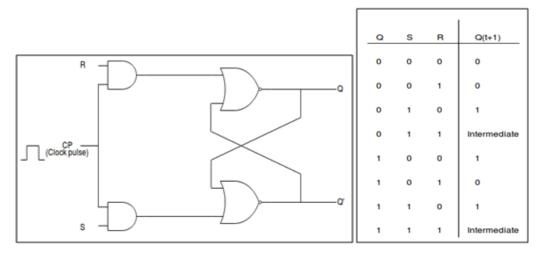

## Clocked S-R Flip Flop

The introduction of the clock signal in the computer circuits has become essential as all the operations of the computer are synchronized with the clock. The clocked SR flip- flop overcomes the undefined state problem of the SR latch. Figure 2.19 shows the circuit for clocked SR Flip- flop which is an extended form of SR latch with two inputs and two outputs, controlled by a clock pulse. The S and R inputs are valid till the clock pulse is high and as soon as the clock pulse becomes low, old outputs Q and Q will remain unchanged and the flip-flop will wait for the next input when the clock pulse will become high.

The major drawback of SR flip-flop is the intermediate state, which is undesirable and occurs when both the inputs S and R are high (1). The output can't be predicted in such a condition.

Figure 2.19 SR Flip- flop Circuit representation and truth table

(**Source**- https://www.javatpoint.com/s-r-flip-flop)

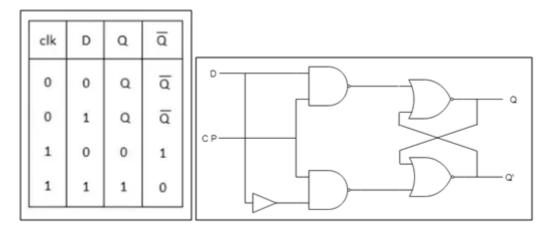

# D Flip- flop

The D flip- flop overcomes the problem of clocked SR flip-flop in which both the inputs S & R cannot be high simultaneously. In D flip- flop, R input is the inverted form of input S that is obtained by putting a NOT gate between S & R inputs as represented in figure 2.20.

Figure 2.20 D Flip- flop truth table and a circuit representation

(**Source**- https://www.javatpoint.com/d-flip-flop)

When the clock pulse is high, the flip- flop is in its SET state and if it is low, the flip- flop adopts a CLEAR mode.

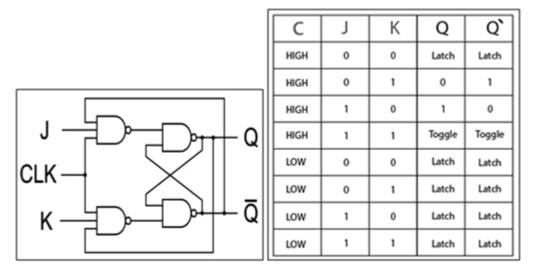

#### JK Flip -flop

JK flip- flop is a modified version of SR flip- flop. The intermediate state of SR flip- flop is eliminated in JK flip-flop. As discussed, when both the inputs in SR flip- flop is high, an intermediate state appears which is eradicated in JK flip- flop. It is done by using an additional feedback system to the SR flip- flop as shown in figure 2.21. In JK flip-flop, when both the inputs J & K are high (1), then the output keeps on toggling itself between the two states using the NAND gates. Toggling of outputs means when Q = 1, it switches to Q = 0 and when Q = 0, it switches to Q = 1.

Figure 2.21 JK Flip- flop circuit representation and truth table